# PROGRESS REPORT ON THE USE OF HYBRID SILICON PIN DIODE ARRAYS IN HIGH ENERGY PHYSICS\*

STEPHEN L. SHAPIRO

Stanford Linear Accelerator Center,

Stanford University, Stanford, CA 94309

and

J. GARRETT JERNIGAN and JOHN F. ARENS

Space Sciences Laboratory,

University of California, Berkeley, CA 94720

#### ABSTRACT

We report on the successful effort to develop hybrid PIN diode arrays and to demonstrate their potential as components of vertex detectors. Hybrid pixel arrays have been fabricated by the Hughes Aircraft Co. by bump-bonding readout chips developed by Hughes to an array of PIN diodes manufactured by Micron Semiconductor Inc. These hybrid pixel arrays were constructed in two configurations. One array format has  $10 \times 64$  pixels, each  $120~\mu m$  square; and the other format has  $256 \times 256$  pixels, each  $30~\mu m$  square. In both cases, the thickness of the PIN diode layer is  $300~\mu m$ .

Measurements of detector performance show that excellent position resolution can be achieved by interpolation. By determining the centroid of the charge cloud which spreads charge into a number of neighboring pixels, a spatial resolution of a few microns has been attained. The noise has been measured to be about 300 electrons (rms) at room temperature, as expected from KTC and dark current considerations, yielding a signal-to-noise ratio of about 100 for minimum ionizing particles.

<sup>\*</sup> Work supported by Department of Energy contract DE-AC03-76SF00515.

Invited talk presented at the Vth International Conference on Instrumentation for Colliding Beam Physics, Novosibirsk, USSR, March 15-21, 1990.

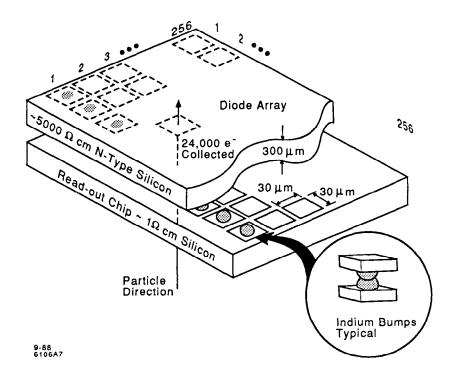

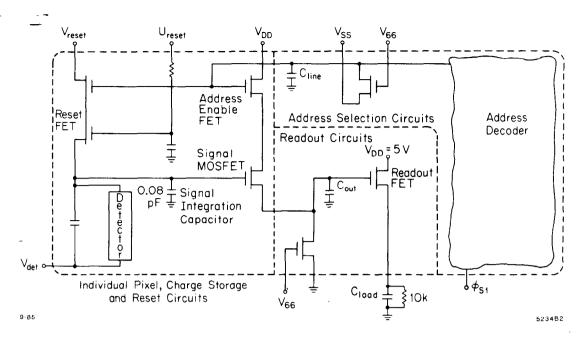

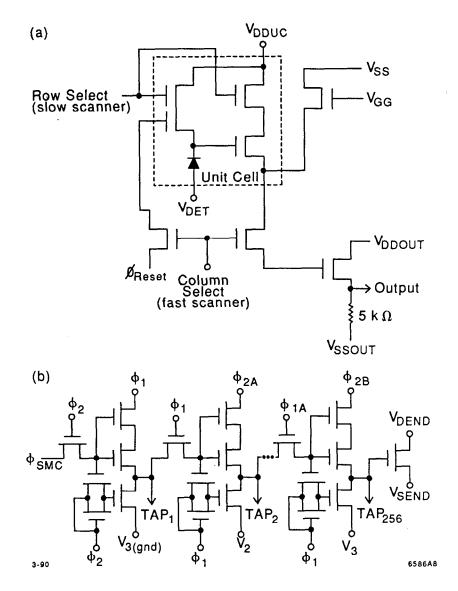

Figure 1: Schematic representation of a silicon PIN diode hybrid detector.

#### Introduction

An architecture well suited for charged particle detection at the SSC is that of a hybrid.<sup>1-3</sup> The charged particle detector and the readout electronics are constructed as two separate silicon chips, each optimized for its specific function. The two chips, indium bump-bonded together, then provide the basic building block for the construction of a detector array.

The choice of the hybrid design (viz., one in which each diode of the detector array is bonded to an independent amplifier readout circuit on a mating VLSI chip via an array of aligned indium metal bumps that cold-weld under pressure to form ohmic contact), allows for additional flexibility in the selection of detector and readout electronics.<sup>4</sup> For instance, a change in the leakage current specification of the detector array will not affect the readout electronics, nor will a change in the VLSI chip oxide thickness to accommodate a radiation hardness specification affect the detector array. Figure 1 is a schematic representation of a silicon PIN diode array hybrid.

### Silicon Hybrid Arrays

Development of hybrid vertex detectors has been the goal of the authors since late 1984. To this end, two hybrid arrays have been designed and fabricated. The

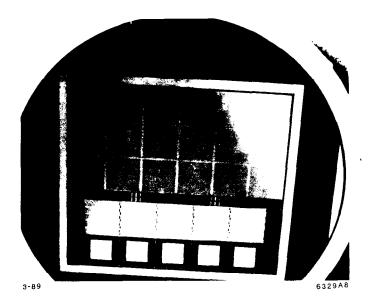

Figure 2: Photograph of a silicon wafer, produced by Micron Semiconductor, containing PIN diode arrays. At the top are  $256 \times 256$  arrays having 30  $\mu m$  square pixels. In the center, are  $1.10 \times 64$  arrays with 120  $\mu m$  square pixels. The square structures at the bottom are test structures.

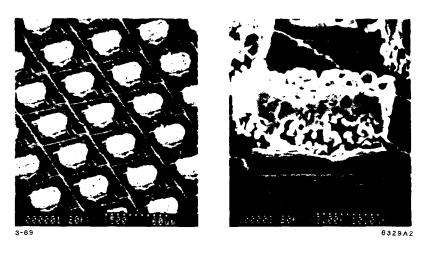

Figure 3: Microphotograph of an array of indium bumps prior to the bonding process.

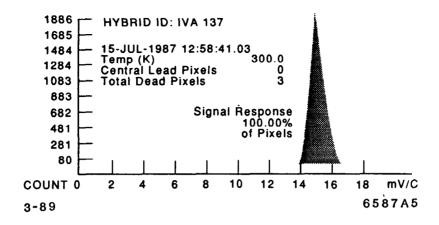

sensor arrays were fabricated by Micron Semiconductor and the readout arrays by Hughes Aircraft. Figure 2 is a photograph of a silicon wafer produced by Micron Semiconductor containing a number of PIN diode arrays of both array geometries. The large squares at the bottom of the photograph are test structures. The indium bump-bonding was done by Hughes with bumps measuring under 15  $\mu$ m in diameter. Figure 3 is a microphotograph of an array of indium bumps prior to the bonding process. Figure 4 is a histogram of the infrared sensitivity of each pixel of a 256  $\times$  256 hybrid array. Note the nearly identical electronic response of the 65,536 pixels of the array and the notation that only 3 pixels in the array are dead. The properties of the two arrays are described in Table I.

Figure 4: A histogram of the infrared sensitivity of each pixel of a 256 x 256 hybrid array.

Table I: Summary of device parameters.

| Array dimension            | $10 \times 64$      | $256 \times 256$        |

|----------------------------|---------------------|-------------------------|

| Pixel size                 | $120~\mu\mathrm{m}$ | $30~\mu\mathrm{m}$      |

| Detector material          | Silicon             | Silicon                 |

| Number of readout channels | 10                  | 2                       |

| Power during "write" cycle | 0 mW                | 0 mW                    |

| Power during read cycle    | $10 \mathrm{\ mW}$  | 2 mW                    |

| Present clock speed        | 1 MHz               | 2 MHz                   |

| Theoretical clock speed    | 10 MHz              | 10 MHz                  |

| Readout mode               | Random access       | Random access           |

| Processing power           | 20 MIPS/channel     | 20 MIPS/channel         |

| Radiation hardness         | 1 Mrad              | ?                       |

| Noise at room temperature  | $<300~e^-~{ m rms}$ | $<300~e^-~\mathrm{rms}$ |

Figure 5 is a schematic diagram of the MOSFET circuit of the  $10 \times 64$  readout array. The diagram has been divided into its several functional portions. The section replicated for each pixel contains four MOSFETs. Signal charge is generated by the detector diode, and is fed to the gate of the signal MOSFET where it stays until a readout is made. The pixel selection circuit indicates how a sequence of address lines can select an individual pixel by turning on the gates of the  $V_{DD}$  bias MOSFET and the enable gate of the reset MOSFET. The  $U_{reset}$  signal allows the gate of the signal MOSFET to be reset to the  $V_{reset}$  level for any pixel that is enabled by the reset MOSFET. All of the signal MOSFETs in a column of the array are connected to a readout MOSFET in a source follower configuration which provides power for driving an external circuit.

Figure 5: Schematic drawing of the readout electronics of the 10 × 64 readout array.

The present readout chips allow random access to any pixel, which then operates as an independent detector. By virtue of its geometry alone, each pixel detector (PIN\_diode) provides about 3,000 times less sensitivity to diode leakage current than a microstrip detector, which will increase the radiation hardness to neutrons. To complement this increase in the radiation hardness of the detector diode, the readout chips can be fabricated in a technology which is radiation hard to 1 Mrad of <sup>27</sup>Co gamma rays at cryogenic temperatures.

The two readout chips are similar, but have some differences. The  $10 \times 64$  array has a random access architecture, in that a unique setting of its address lines will select one and only one row of pixels. The  $256 \times 256$  array, on the other hand, is random access in that the pixels are addressed via row and column shift registers. This feature makes addressing a given pixel more complicated but allows easy implementation of a sparse scan algorithm. This particular readout chip has been optimized to collect electrons but is bipolar at the signal levels we expect.

### Description of Present Hardware

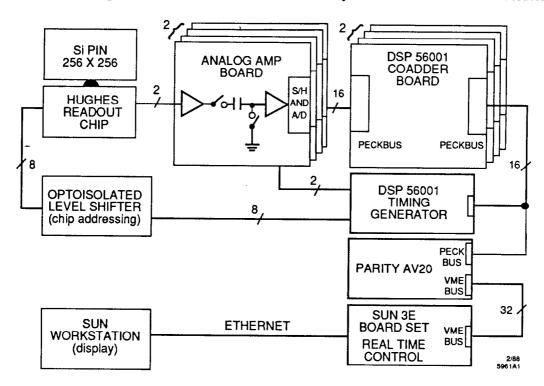

Figure 6 is a photograph of the  $10 \times 64$  array in its mount in the laboratory. Figure 7 is a block diagram of the high energy physics data acquisition system. This system, used to read out the  $256 \times 256$  array, is more modern and more upto-date than the system described in Ref. 2, on which the  $10 \times 64$  data described in this paper were taken. A Sun Microsystems Sun-3/110LC-4 workstation controls a system housing a Sun 3/E CPU, a Motorola 68020 bus converter board, amplifiers, ADCs, digital signal processors, and a clock generator. The digital signal processor

Figure 6: A photograph of the 10 × 64 silicon PIN diode hybrid in its mount in the laboratory.

Figure 7: A block diagram of the high energy physics readout and display electronics.

is the Motorola DSP56001. This device acquires data at a rate of 10 MIPS, processes it, and passes it, via the MC68020 to the Sun 3/E. The bus converter board, a Parity systems AV20 dual port processor, interfaces the local analog bus (PECKBUS) to the VME bus.

Detector Development funds were used to begin the fabrication of the dedicated high energy physics data acquisition system described above. The amplifier/ADC/DSP56001 boards and the clock generator in the present system, however,

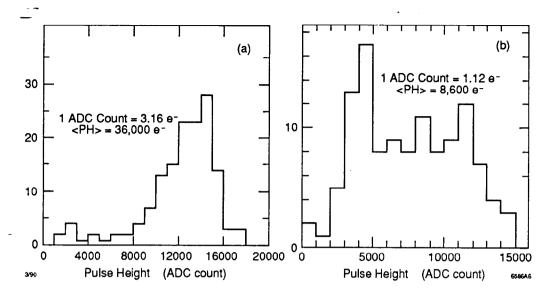

Figure 8: (a) The pulse height spectrum of the alpha data; and (b) the pulse height spectrum of the beta data.

are circuits remaining from the infrared data acquisition system. These need to be redesigned to high energy physics criteria.

A data acquisition and display software package based on the previous system has been written. The operating system is UNIX; the DSP has been programmed in assembly language; and various control functions are written in Magic/L, an interactive language derived from Forth. The Parity AV20 dual port processor has been programmed in C, and the DSP will be reprogrammed in C.

# Radioactive Source Testing of the Arrays

Testing of the  $10 \times 64$  hybrid array started in mid-September 1989 at the Space Sciences Laboratory in Berkeley, while testing of the  $256 \times 256$  array started in December 1989 at Hughes Aircraft, Carlsbad.

A  $^{106}$ Ru beta source and an  $^{241}$ Am alpha source were used to irradiate the  $10 \times 64$  array. Spectra for both alphas and betas were obtained, and the data are presented in Fig. 8. From this data, we roughly calculate both the signal in the hit pixels and the noise in the surrounding pixels. We have verified that both signal and noise agree with models of the readout electronics.

In our geometry, particles enter the device on the cathode of the PIN diode, the side farthest from the bump-bonds. Thus, much of the charge collected must drift across the entire depletion distance of 300  $\mu$ m. The charge cloud, spread by scattering of the initial radiation and by diffusion, will have a finite lateral size. If a particle were closer to the edge of a pixel than to the center, one would expect charge to be shared by adjacent pixels. On average, we see charge spread over 9 pixels; a  $3 \times 3$  array.

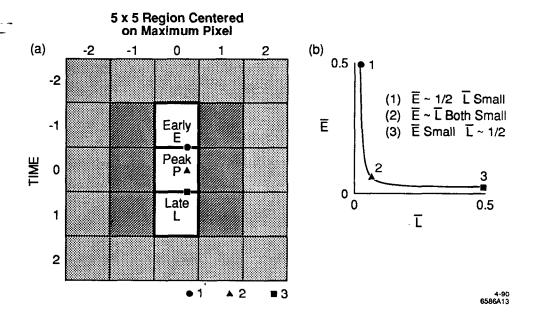

Figure 9: (a) A schematic of a  $5 \times 5$  pixel region centered on a particle hit; and (b) a schematic plot of the  $\overline{E}$  versus  $\overline{L}$  plane indicating the result of various hypothetical incident positions of a particle within the central pixel.

A detailed analysis of a set of pixels near a particle hit allows the calculation of four quantities: signal-to-noise, noise, size of the charge cloud, and spatial resolution. In Fig. 9(a), a schematic of a  $5 \times 5$  region centered on a particle hit is shown. The pixel with the maximum signal is located at (0,0) is labelled "PEAK" and the pulse height of its signal referred to as P. Nearby pixels are located by offsets between -2 and +2. Each pixel in the  $5 \times 5$  region has its zero set by analyzing other frames of data wherein there have been no particle hits in its vicinity. Further, in analyzing a particular hit, an average of the outer border of 16 pixels is subtracted from the inner 9 pixels to remove any systematic offset which arises because of the separation in time between the measurement of the background frame and the frame containing the particle hit. The direction of time in Fig. 9(a) refers to the sequence of the readout of the pixels. In this device, columns are read out in parallel, thus, the five pixels in the row labeled -2 at the top of the figure are read out first, with sequential readout, by row, from -2 to +2 on the time axis. For convenience, the pixel just above the PEAK is labelled "EARLY," and its contents referred to as E, while the pixel just below the PEAK is labelled "LATE," and its contents referred to as L.

E, P, and L are used to derive the  $\overline{E}$  and  $\overline{L}$  ratios from the relation:

$$\overline{E} = E/(E+P+L)$$

and  $\overline{L} = L/(E+P+L)$ .

Figure 9(b) is a schematic plot in the  $\overline{E}$  versus  $\overline{L}$  plane of what should happen if a particle were to hit different parts of the central pixel. Possibilities 1, 2, and 3 are

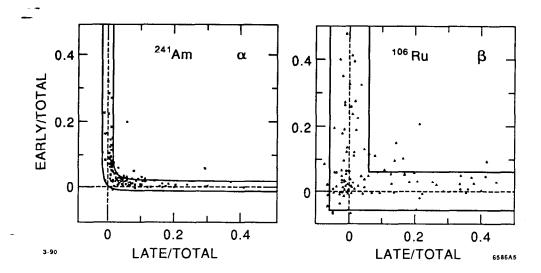

Figure 10: A scatterplot of charge sharing for incident alpha and beta radiation incident on the  $10 \times 64$  array. The  $\pm 2\sigma$  limits are shown as solid lines.

indicated in the central pixel, with their corresponding results shown in Fig. 9(b). The position of possibility 2 will be close to or far from the origin depending on the size of the charge cloud.

Figure 10 shows the  $\overline{E}$  or EARLY/TOTAL versus  $\overline{L}$  or LATE/TOTAL scatterplots for the alpha and beta data. The trend of the data to fall near the axes, as explained schematically by Fig. 9(b), is as expected. The difference in the two cases is dominated by the somewhat larger charge cloud generated by the alphas compared to the betas. If one uses the measured signal-to-noise of the total charge deposited by a particle hit, one can derive the expected deviations from perfect correlation in the  $\overline{E}$  versus  $\overline{L}$  plane. The  $\pm 2\sigma$  limit curves for the alpha and beta data are shown in Fig. 10. Note that the data scatter approximately as expected. These curves are not fits to the data shown, but are instead predicted from the signal-to-noise ratio only.

In Fig. 10, the data points near the ends of the L-shaped locus of points represent data which have no charge deposition in either the LATE or EARLY pixel. Thus, the variance of these data is a measure of the fluctuation of the ratio of the signal of a typical nonhit pixel and the total signal from the three pixels in a hit column. This variance is the inverse of the average signal-to-noise ratio. For this analysis, the variance of  $\overline{E}$  for data where  $\overline{L} \geq 0.25$ , and the variance of  $\overline{L}$  for data where  $\overline{E} \geq 0.25$  is used. The signal-to-noise ratio for the beta sample from this variance is about 36. The same analysis for the alpha data set yields a signal-to-noise ratio of 113. The mean signal size for the betas is about 8,600 electrons, while that for the alphas is 36,000. Thus, the two independent measurements of noise yield 239 and 319, respectively, for the beta and the alpha data. The error in making this measurement is not statistical, but is dominated by systematic errors, estimated to be at the 20% level. Thus, for both alphas and betas, the noise measurement corresponds to about 300 electrons (rms).

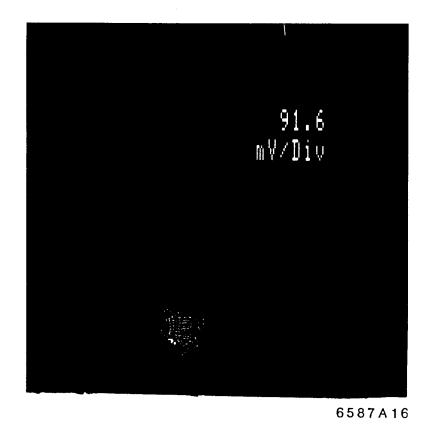

Figure 11: Image of a laser spot on the face of the  $256 \times 256$  array.

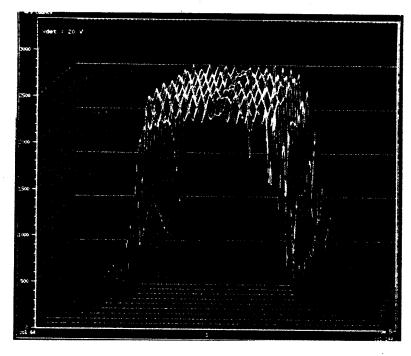

Figure 12: Three-dimensional plot of the pulse height recorded by each pixel of the array when illuminated by the laser spot.

The noise measurements are somewhat higher than a calculation of KTC noise and dark current noise, which are the dominant sources of noise at room temperature. For our devices, these are 110 electrons (rms) and 120 electrons (rms), respectively, yielding a combined noise of 165 electrons (rms). We attribute this extra noise to the external electronics, and expect that it can be removed by better calibration and filtering. We have, however, achieved our goal of 300 electrons (rms) at room temperature.

From the ratio of the number data points which lie near the axes and the number of data points in the cluster near the origin, one can determine the average size of the charge cloud produced by an incident charged particle. For betas, this size is 19  $\mu$ m (1 $\sigma$ ) and for alphas this size is 28  $\mu$ m (1 $\sigma$ ), assuming a two-dimensional Gaussian profile.

To determine the spatial resolution, one uses the fact that the cluster of data points near the origin corresponds to events which deposit nearly all of their charge in the central pixel. Thus, within this region, no interpolation is possible. For those events which are near the edge of a pixel, one can use the variance noted earlier to estimate the error in the position within the pixel. For the betas which strike within 30  $\mu m$  of an edge, the centroid of the 19  $\mu m$  distribution can be located to within about 2  $\mu m$ . A similar result for the alphas is 2–3  $\mu m$  across the entire 120  $\mu m$  pixel, due to the larger size of the alpha induced charge cloud.

Preliminary testing of the  $256 \times 256$  array has been started in the test laboratory of Hughes Aircraft in Carlsbad, California. In this test station, flexibility has been emphasized over a high data rate. Data has been acquired at a 60 Hz frame rate, resulting in a 500 ns pixel read time. To check out the test station and the hybrid array initially, light from a low-power neon laser was focused onto the array cathode via a crude pinhole. The resulting image shown in Fig. 11 could be seen to move across the array surface as the laser was moved. Figure 12 is a three-dimensional plot of the pulse height during this test.

Figure 13(a) is a schematic diagram of the MOSFET circuit of one cell of the  $256 \times 256$  array, and Fig. 13(b) is a schematic of the six transistor slow shift register. The fast shift register enjoys the same circuit configuration, but has transistors of slightly different geometry.

The bulk of the preliminary data on this hybrid was taken at 200 °K. The hybrid evidenced dark current at room temperature at twenty times the expected level. Rather than wait for a new hybrid, it was felt that characterizing the existing chip, cold, would be more instructive.

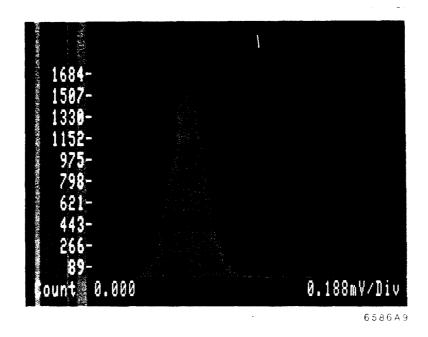

Figure 14 is a measurement of the noise for this hybrid at 200 °K. Sixteen frames of data were taken and a pixel-by-pixel average taken at the normal frame rate of 60 Hz. The data displays the average pulse height at the output of the chip in mV. The truncated mean is about 3.5 divisions at 0.188 mV/div. Using a pixel capacitance of 40 fF, one calculates the noise to be 165 electrons (rms) at this temperature. KTC noise is about 65 electrons (rms) and the dark current is negligible at these temperatures. This data was taken with no double-correlated sampling techniques used; thus, other sources of noise such as 1/f noise remain in the measurement.

Figure 13: (a) A schematic diagram of the MOSFET circuit of one cell of the  $256 \times 256$  array; (b) a schematic diagram of the six transistor slow scanner.

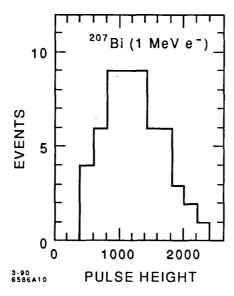

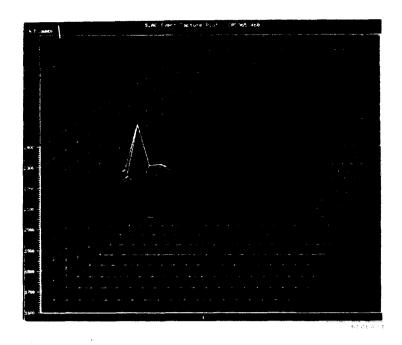

The array was exposed to radiation from a  $^{207}$ Bi source. This provides a source of 1 MeV electrons, which directly give a measurement of the signal to be expected from minimum ionizing particles. Figure 15 is a spectrum of the radiation from the Bismuth source. The 1 MeV electrons will result in 24,000 electron hole pairs (channel 1000 in Fig. 15) if they transit the PIN diode detector array normally. However, due to multiple Coulomb scattering, they will certainly not do this, but rather will exit the bottom of the array after scattering through an angle of about 38 degrees, and going through about 380  $\mu$ m of material. This will result in an average pulse height of about 30,000 electrons hole pairs (channel 1200).

Figure 14: A noise spectrum of the  $256 \times 256$  array at 200 °K.

Figure 15: The pulse height spectrum measured using the  $256 \times 256$  array when irradiated by a  $^{207}$ Bi source, emitting 1 MeV electrons, and a number of gamma rays.

The explanation for the pulse height distribution which occurs below channel 1,000 is found in the myriad of gamma rays which also are produced by the Bismuth source. For every 100 Bismuth decays, one gets 9–1 MeV electrons; but one also gets: 100–574 KeV gammas, 75–1 MeV gammas, 75–(70–90) KeV gammas, and 30–(10–13) KeV gammas. When all of these gamma rays are multiplied by their respective conversion probabilities in 300  $\mu$ m of silicon, one observes that for every 100 Bismuth decays one sees: 1 event from the 175 high energy photons, 9 events

...Figure 16: A three-dimensional plot of a 1 MeV electron being detected by the 256 x 256 array.

3-89 6329A4

Figure 17: A photograph of a  $256 \times 256$  silicon hybrid array similar to the one used in these measurements.

from the 1 MeV electrons, and 10 events from the 70–90 KeV photons. There are no events recorded from the low-energy photons, as we set a threshold of about 6,250 electron-hole pairs for this data set. Figure 16 is a three-dimensional plot of a characteristic minimum ionizing particle event. Figure 17 is a photograph of a  $256 \times 256$  silicon PIN diode hybrid similar to the one used for these measurements.

#### The Future

We intend to continue our program of testing hybrid arrays in the laboratory. We are also scheduled to test these devices in high energy beams at Fermilab later this year.

Throughout 1990, we will continue our efforts to design a single board readout system which has all of the features necessary for a high energy physics array readout. We will also be continuing our efforts, as members of a larger collaboration, to design and fabricate a large array suitable for use at the SSC. This new array is to have small pixel size, low noise, and the ability, called time tagging, to signal the occurrence of a hit within the array with a time resolution of about 50 ns. It will also demonstrate the ability to be completely read out in a few microseconds using a sparse scanning algorithm.

We will be working hard on issues of mounting, cooling and aligning these arrays, and on their suitability for use in other venues such as the B Factory, recently proposed at SLAC. Lastly, the suitability of these arrays for investigations at synchrotron radiation light sources is being studied.

## Summary of Results

Room-temperature operation of the  $10 \times 64$  arrays has been demonstrated with noise-levels less than 300 electrons (rms). Charged particles have been detected and imaged using this array with excellent signal-to-noise, and a preliminary measurement of 2–3  $\mu$ m spatial resolution has been achieved. A measurement of the noise in the 256  $\times$  256 array has been made at 200 °K, and found to be about 165 electrons (rms). Charged particles have been detected and imaged and pulse heights consistent with those expected have been achieved.

#### References

- 1. S. Shapiro and T. Walker, "The Microdiode Array—A New Hybrid Detector," SLD New Detector Note No. 122 (1984).

- S. Shapiro, W. Dunwoodie, J. Arens, J. Gernigan, and S. Gaalema, "Silicon PIN Diode Array Hybrids for Charged Particle Detection," Nucl. Instrum. Methods A275 (1989) 580.

- 3. S. Gaalema, G. Kramer, S. L. Shapiro, W. Dunwoodie, J. Arens, and J. G. Jernigan, "Silicon PIN Diode Hybrid Arrays for Charged Particle Detection: Building Blocks for Vertex Detectors at the SSC," *Proc. Int. Industrial Symposium on the Supercollider*, 1989, New Orleans, LA, p. 173.

- 4. S. Gaalema, "Low Noise Random-Access Readout Technique for Large PIN Detector Arrays," *IEEE Trans. on Nucl. Sci.* NS-32, No. 1 (1985) 417.