# FASTBUS DUAL-PORT MEMORY AND DISPLAY DIAGNOSTIC MODULE\*

BORIS BERTOLUCCI

Stanford Linear Accelerator Center, Stanford University, Stanford, CA 94305

## ABSTRACT

• A dual-port FASTBUS memory module has been designed as a diagnostic tool for both Crate and Cable Segments.

## INTRODUCTION

The module described here is a FASTBUS slave module with ports to Crate and to Cable Segments. It incorporates two.distinct but interlaced memories: one  $(256 \times 32 \text{ bits})$  is a fast memory (10 nsec access time) used for testing the busses at full FASTBUS speed; the other one is a slower, larger memory (16k  $\times$  32 bits with 100 nsec access time) for software testing purposes.

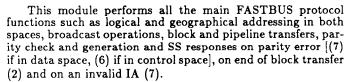

The module performs all the main FASTBUS protocol functions. It is designed using KEK's FMA601 ADI chips and SLAC's hybrid prototypes of a cable segment differential transceiver.

#### DESCRIPTION

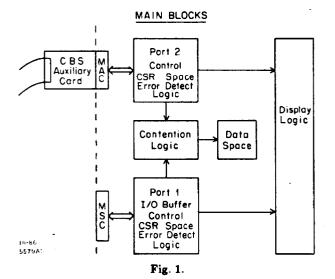

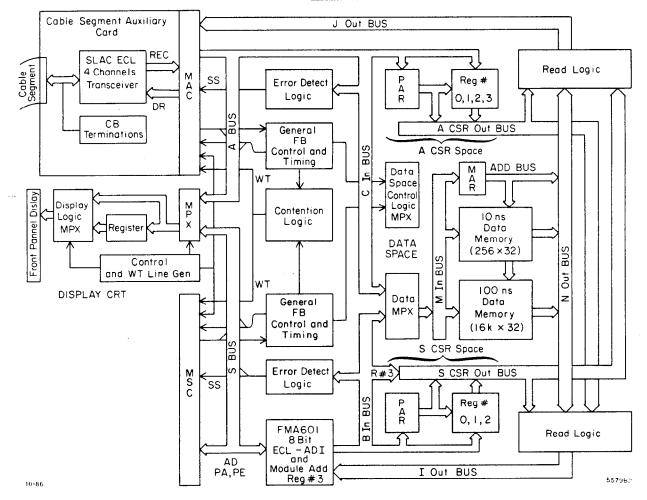

The module can be subdivided in six main blocks (Fig. 1) as follows.

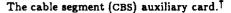

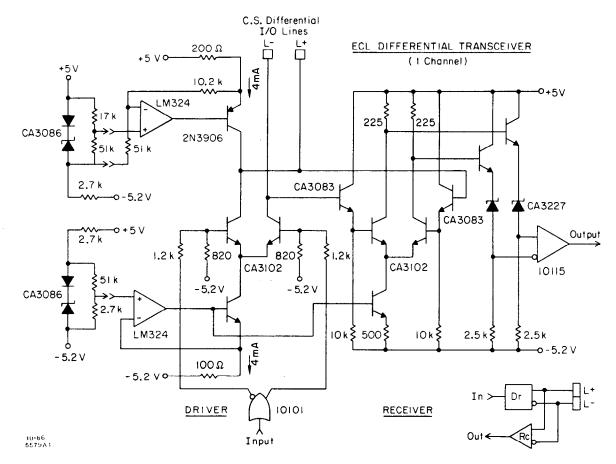

The CBS Auxiliary Card (Fig. 2 and Photo A) is a  $6\frac{1}{4} \times 6\frac{7}{8}$ inch card and accommodates 15 four-channel SLAC ECL Differential Transceivers, terminations for the driver input lines (LT), terminating resistors and bias current sources for the CBS differential lines (CST)<sup>1</sup>. Depending on the position of the module on the Cable Segment, different combinations of resistor packages can be used to terminate the cable at the passive end (100  $\Omega$  between the lines) or at the active end (two 51  $\Omega$  to V<sub>term</sub> and a bias current I on the L+ line) or nothing at all at other locations. The resistor values chosen terminate a cable with a characteristic impedance of 100  $\Omega$ .

<sup>†</sup> The Working Group on FASTBUS Cable Segment recommended a preferred method of "outboarding" cable segment drivers and receivers on an auxiliary card so that a module can survive potential changes in Cable Segment specifications (Atlanta July 1, 1986). In this scheme, the A pins of the Auxiliary connected to the Receiver Outputs while the B pins shall be connected to the Driver Inputs.

A resistor of 1.3K  $\Omega$  to  $V_{EE}$  provides a 4 mA current sink. For a 4 mA system the error due to the resistor type current 2.8% with a full loaded segment (32 devices). Note that, due to the common mode range of the receiver, the terminating voltage  $V_{term}$  is zero (GND).

Photo A.

Figure 3 shows the implementation of the SLAC Differential Transceiver which has been described elsewhere<sup>2</sup>.

## Port 1 or crate port.

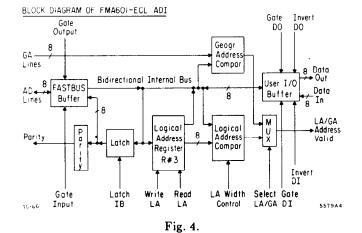

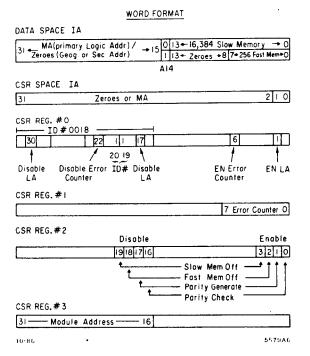

This part includes four FMA 601-ECL ADI chips, CSR Registers, error detection logic and control logic for the Crate Port. The ADI chip (Fig. 4) has bidirectional buffers for the AD lines and unidirectional buffers for the user, Parity generation logic, Logical Address Register CSR#3 and Logical and Geographic Address comparators. CSR space includes Reg.#0 (ID Reg.), Reg.#1 (Error Counter), Reg.#2 (Control Reg.), and Reg.#3 (Module Addr. (MA) Reg. in the ADI).

## Port 2 or cable port.

This part is a symmetrical copy of Port 1 less the ADI chips (the I/O buffering for the AD lines is done by the transceiver) plus an external Module Address Register CSR Reg.#3, Geographical and logical Address comparators and register latches for data read.

• • • • • • • •

<sup>\*</sup>Work supported by the Department of Energy, contract DE-AC03-76SF00515.

## Data space.

This portion is shared by both ports. It includes a 14 bit Memory Address Register (MAR) and the two memories: a fast  $256 \times 32$  bit memory (Fujitsu MBM 10422) with 10 nsec access time and a slow  $16k \times 32$  bit memory with 100 nsec access time (Hitachi HM 6264LP-10).

# Contention logic.

This part resolves contention between the crate port and the cable port when both try to access Data Space. When Data space has been accessed by one port, the other port is held off and a WT signal will be issued to that port by the contention logic if it tries to access this space.

# Display logic (Fig. 5).

This logic ten mention either ber continued, (- mitch selects crate or cable bus) or can generate WT in response to selected leading or trailing edges of the timing signals AS, AK, DS, DK and AG and at the same time latch the content of that bus into internal registers. It has manual or automatic (variable, up to 1 sec) reset capability on the WT line. Front panel LED display is switch selectable to show either the content of the internal registers or the status of the bus after the WT line has been received by the operating modules and activity has stopped.

#### OPERATION

Each port has always complete control of its own CSR space. It can also read all the CSR space Registers of the other port at any time with one exception: Port 2 can access Reg.#3 of Port 1 only if Port 1 is not busy. This is due to the fact that Reg.#3 (MA reg.) is inside the ADI chip. Data Space is shared by both Ports and the contention logic will permit access to this space on a first-come-first-serve basis.

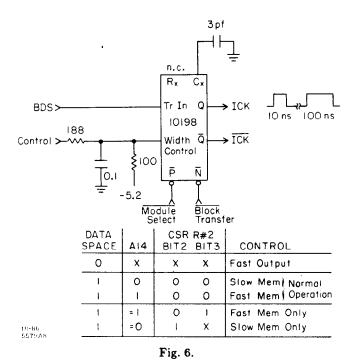

Data space can be organized as one fast  $256 \times 32$  bit memory, one slow 16K imes 32 bit memory, or the combination of both. Two control bits in CSR Reg. #2 may disable access to either one of the memories or none. In the latter case the fast memory follow the slow one. Wrap-around occurs in all three cases, though a SS=2 signal is generated with overflow. A dual-width clock generator is needed to access the two memories. Figure 6 shows how this generator has been implemented. The chip used is the MC10198 retriggerable one-shot, the trigger comes from the Fastbus Data Synch (DS) line (buffered and delayed). The positive (P) and negative (N) edge control lines are driven by module select (internal AK line) and block transfer (MS0=1) signals respectively, the width control input is controlled, through a resistor divider, by the two control lines (bit 2 and 3) of CSR Reg.#2 and the Address line A14. A logical "0" at this input produces 10 nsec clock pulses, a logical "1" yields 100 nsec clock pulses.

Figure 7 shows a detailed block diagram of the module, Fig. 8 the word formats and Photo B a prototype module.

The implementation is done in ECL eccept for the TTL 16K memory and related translators.

# APPLICATIONS

This module is extremely valuable as a diagnostic tool. It can be used for error logging, general debugging including block transfers, for monitoring either segment on-line through the front panel display, and to facilitate the testing of master modules at full ECL speed.

It not only permits the detailed examination of both segments, but it also has a sufficiently large and fast memory to allow many diagnostic tests to be made, or to serve as a communication "mailbox" between segments.

## ACKNOWLEDGMENTS

The author acknowledges the contributions made by O. Darton, J. Holgers, J. Manarti, J. Mars, R. Dartiste and the Publication Staff of SLAC.

# BLOCK DIAGRAM

Fig. 7.

Fig. 8.

Photo B

#### REFERENCES

- 1. IEEE Standard FASTBUS Modular High-Speed Data Acquisition and Control System, ANSI/IEEE Std 960-1986 (Appendix C).

- 2. B. Bertolucci, Transceiver for the Fastbus Cable Segment, IEEE Trans. 1984 NSS, Vol. NS-32, No. 1, 1985.

-

- 3. B. Bertolucci and D. Horelick, Design of a Fastbus Programmable Sequencer Module and Memory Module, IEEE Trans. 1981 NSS, Vol. NS-29, No. 1, 1982.

- 4. B. Bertolucci, Modules and Supporting Hardware for Fastbus Test and Diagnostic Purposes, IEEE Trans. 1981 NSS, Vol. NS-29, No. 1, 1982.