# Fine Pixel CCD Option for the ILC Vertex Detector

19 Mar. 2005 @LCWS2005

Y. Sugimoto

KEK

#### **Vertex Detector Options**

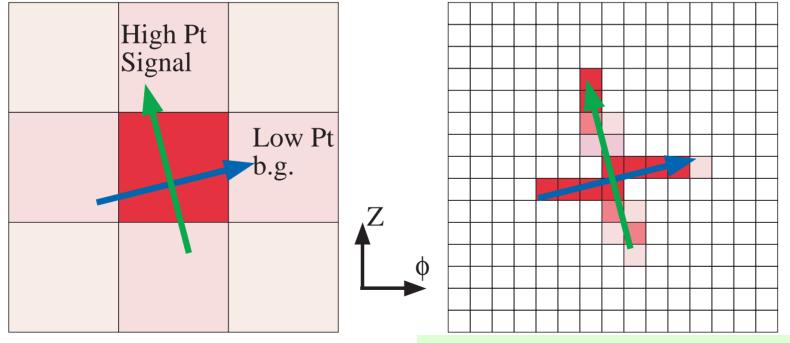

- If the hit signal is accumulated for one train of 2820 bunches, too many hits by beam b.g. → for 25 µm pixels, the pixel occupancy > 20%

- Solutions;

- Fast readout : Column Parallel CCD @50MHz, 20 frames/train

- Possible effect by RF noise by beam

- Analog registers in each pixel (~20/pixel), and readout between trains

- CMOS: Flexible Active Pixel Sensor (FAPS)

- CCD: In-situ Storage Image Sensor (ISIS)

- Complicated structure → Large area OK?

- Make pixel density x20 → Fine Pixel CCD (FPCCD)

#### **Vertex Detector Options**

#### • FPCCD

- Accumulate hit signals for one train and read out between trains

- Keep low pixel occupancy by increasing number of pixels by x20 with respect to "standard" pixel detector

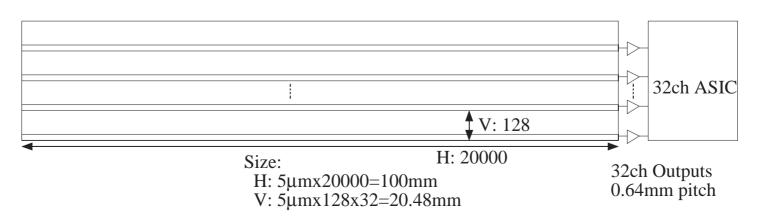

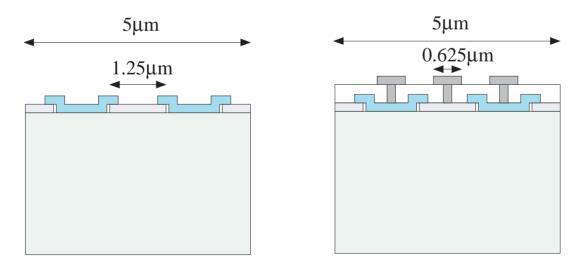

- As a result, pixel size should be as small as  $\sim 5 \times 5 \mu m^2$

- Epitaxial layer has to be fully depleted to minimize charge spread by diffusion

- Operation at low temperature to keep dark current negligible (r.o. cycle=200ms)

## **Advantages of FPCCD**

- Free from beam-induced RF noise

- $\sigma_x \sim 1.4 \mu m$  even with digital readout

- Simple structure : advantageous for large size

- Active circuit on one edge : easy to control temperature

- Readout speed: 15MHz is enough (128(V)x20000(H)/200ms=12.8MHz) (CPCCD:>50MHz)

## **Challenges of FPCCD**

- <u>Pixel size</u>

- Horizontal register in image area

- Tracking efficiency

- Thin wafer and support structure

- 50μm thick, 20x100mm<sup>2</sup>

- Lorentz angle

- Low B is preferable

- Readout electronics

- Signal level is small (~500 e)

- Radiation hardness

- Relaxed by low temp. operation

E

#### **Pixel Size**

- 5µm pixel of fully depleted CCD has full-well capacity of only few k electrons

- CCD process

- 5µm pixel with poly-Si gate is easy (1.6µm pixel CCD for cameras on mobile phone already exists)

- Large size and fast readout require Al layer

- Large size CCD with 5µm pixel with poly-Si gate and metal layer is not easy

- In FPCCD, pixel occupancy would be low (~1%) but hit density mainly due to the pair-background is as high as ~40/mm<sup>2</sup> (B=3T, R=20mm, L=3.4x10<sup>34</sup>)

- So, it is not trivial whether we can get good tracking efficiency

- Extrapolation of tracks from Si intermediate tracker (SIT) with bunch ID capability will be necessary

- The study of tracking efficiency under high background rate is the most important and urgent issue

- Simulation framework to overlap background hits with physics events has to be constructed

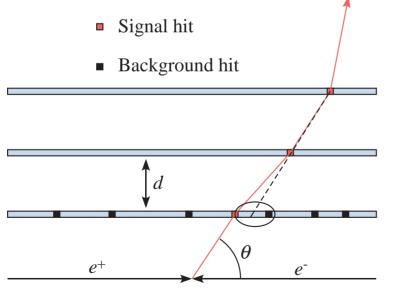

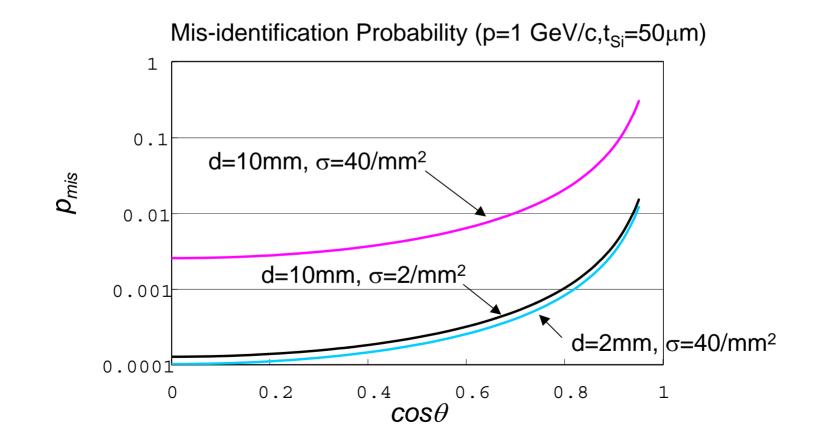

Large number of background hits may cause tracking inefficiency: mis-identification of signal hit with background hit

For a normal incident track, the probability of mis-identification of hit is given by;

$$p_{mis} = 2\pi\sigma R_0^2, R_0 = d\theta_0$$

$\sigma$ : Background hit density  $\theta_0$ : Multiple scattering angle

Angular and momentum dependence;  $p_{mis} \propto p^{-2} \sin^{-4} \theta$

- Some ideas for b.g. rejection (1)

- CCD doublet in proximity to reduce effect of M.S.

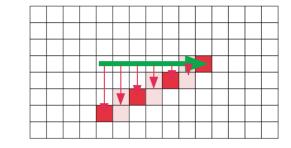

- Some ideas for b.g. rejection (2)

- Hit cluster shape

(tracking capability with single layer!)

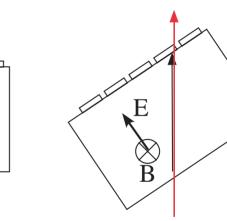

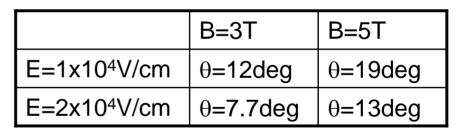

#### **Lorentz Angle**

- Lorentz angle in depleted-layer

- tanθ=μ<sub>n</sub>B

μ<sub>n</sub>: electron mobility

- Carrier velocity saturates at high E field:

- μ<sub>n</sub> =0.07 m<sup>2</sup>/Vs

@T=300K, E=1x10<sup>4</sup>V/cm

- μ<sub>n</sub> =0.045 m<sup>2</sup>/Vs

@T=300K, E=2x10<sup>4</sup>V/cm

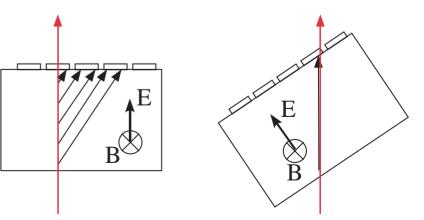

- Small angle can be cancelled by tilting the wafer

- May not be a serious problem

- Number of hit pixels does not increase so much

#### **Study Issues of FPCCD**

- Simulation study

- Tracking efficiency

- Physics implication (Flavor tagging)

- Hardware study (depends on funding)

- Charge spread in fully depleted CCDs

- Lorentz angle in B field → Optimization of wafer tilt angle

- Radiation hardness (difference in fully depleted CCD?)

- Show that FPCCD works as a vertex detector "in principle"

- Mid term goal (by "CDR")

- Fabrication of prototype ladders

- Test the prototypes and demonstrate the performance

- Long term goal (by "LOI")

- Engineering design of FPCCD Vertex Detector

#### Summary

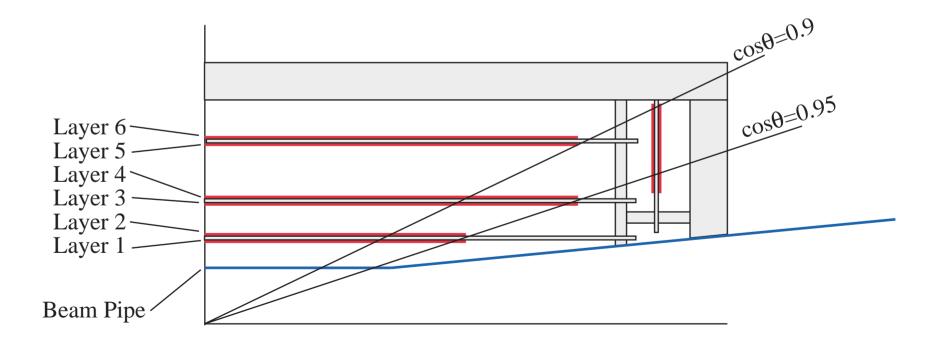

- We propose FPCCD option for the ILC Vertex

Detector

- Fully depleted CCD with 5µm-square fine pixel size

- Accumulate 2820 BX and readout between trains

- Two layers make a doublet (super layer) to pick up signal hits out of background hits

- FPCCD seems the most feasible (least challenging) technology among the proposed options

- Tracking efficiency under beam background is the most critical issue for FPCCD. Simulation study is urgent.