# **Analysis and Performance of Computer Instruction Sets**

Leonard J. Shustek

SLAC-R-205

Prepared for the Department of Energy under contract number DE-AC02-76SF00515

Printed in the United States of America. Available from the National Technical Information Service, U.S. Department of Commerce, 5285 Port Royal Road, Springfield, VA 22161.

This document, and the material and data contained therein, was developed under sponsorship of the United States Government. Neither the United States nor the Department of Energy, nor the Leland Stanford Junior University, nor their employees, nor their respective contractors, subcontractors, or their employees, makes an warranty, express or implied, or assumes any liability of responsibility for accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use will not infringe privately owned rights. Mention of any product, its manufacturer, or suppliers shall not, nor is it intended to, imply approval, disapproval, or fitness of any particular use. A royalty-free, nonexclusive right to use and disseminate same of whatsoever, is expressly reserved to the United States and the University.

# ANALYSIS AND PERFORMANCE OF COMPUTER INSTRUCTION SETS

#### A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE

AND THE COMMITTEE ON GRADUATE STUDIES

OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

By

Leonard Jay Shustek

January 1978

#### **ACKNOWLEDGMENTS**

I would like to thank my thesis advisor, Forest Baskett, for his inspiration, advice, and patience. I would also like to thank the other members of my committee -- John Wakerly and Gio Wiederhold -- for their careful and constructive reading of the thesis.

I especially want to express my gratitude to Bernard Peuto for being a critic, confidant, and friend when I needed it most.

Most of this work was done in the Computation Research Group of the Stanford Linear Accelerator Center, supported by the U.S. Department of Energy under contract E(043)515.

# TABLE OF CONTENTS

| knowledgments iii                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| apter page                                                                                                                                                                                                               |

| INTRODUCTION 1                                                                                                                                                                                                           |

| Scope                                                                                                                                                                                                                    |

| PREVIOUS WORK                                                                                                                                                                                                            |

| System-Level Performance Evaluation                                                                                                                                                                                      |

| II. INSTRUCTION TIMING MODEL FOR MACHINE EVALUATION                                                                                                                                                                      |

| The Model The Technique Evaluation of Important Factors Instruction Timing Formulas Measurement Approximations Description of the Measurement System Verification Cache Miss Penalty SVC Times Benchmark Jobs Validation |

| V. CHARACTERISTICS OF THE IBM 370 ARCHITECTURE 55                                                                                                                                                                        |

| Opcode Distributions                                                                                                                                                                                                     |

|      | Register Use Operand Lengths LM/STM Character Instructions Decimal Instructions Memory Reference and Cache Effects Pipeline Effects for the 470 Summary | 81<br>82<br>83<br>86<br>88<br>89                                |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| v.   | OTHER ARCHITECTURE CHARACTERISTICS                                                                                                                      | 92                                                              |

|      | Summary                                                                                                                                                 | 94<br>95<br>99<br>102<br>103<br>104<br>105<br>105<br>108<br>109 |

| VI.  | PREDICTIVE MODELS                                                                                                                                       |                                                                 |

|      | 370 Branch Improvement                                                                                                                                  | 118<br>126                                                      |

| VII. | ARCHITECTURAL CONCLUSIONS                                                                                                                               | 139                                                             |

|      | Time is of the Essence                                                                                                                                  | 143<br>145<br>147<br>148<br>148                                 |

|      | The Consequences of Small Execution Distances                                                                                                           |                                                                 |

|      | Address Displacement Size Should Be Large Are There Missing Instructions? The Effect of Task Switches on Cache                                          | 153<br>153                                                      |

|      | Contents                                                                                                                                                | 154<br>156                                                      |

| Appe | ndix                  |           |

|------|-----------------------|-----------|

| Α.   | INSTRUCTION MNEMONICS | • • • • • |

|      | IBM 370 Instructions  | • • • • • |

•

.

.

# LIST OF TABLES

| Table | e page                                                     |

|-------|------------------------------------------------------------|

| 1.    | SVC Times and Cache Requests 45                            |

| 2.    | Program Characteristics 49                                 |

| 3.    | Predicted and Benchmark Times 53                           |

| 4.    | Instruction lengths 68                                     |

| 5.    | Branch Instructions 69                                     |

| 6.    | Instructions Which Caused Branches, Sorted By Frequency 71 |

| 7.    | Execution Distances                                        |

| 8.    | Opcode Pairs 75                                            |

| 9.    | Register Use for RX Instructions 81                        |

| 10.   | 8080 Dynamic Instruction Statistics 94                     |

| 11.   | 8080 Dynamic Opcode Pairs 98                               |

| 12.   | 8080 Static Opcode Pairs                                   |

| 13.   | Types of 8080 Jumps                                        |

| 14.   | 8080 Execution Distance                                    |

| 15.   | Pascal P-CODE Opcode Pairs                                 |

| 16.   | PDP11 Addressing Modes - All Operands (Static) 109         |

| 17.   | PDP11 Addressing Modes - By Operand (Static) 112           |

| 18.   | PDP11 Two-operand Addressing Modes 112                     |

| 19.   | Special Uses of PDP11 MOV/MOVB 114                         |

| 20.   | Special Uses of PDP11 2-Operand Instructions 115           |

| 21.   | Branch Prediction Success For The 168 120                  |

| 22. | Branch Success as a Function of Branch Direction      | 12] |

|-----|-------------------------------------------------------|-----|

| 23. | Conditional Branch Consistency and Prediction Success | 123 |

| 24. | Branch Prediction Success vs. Number of Executions    | 123 |

| 25. | Measured vs Predicted Execution Distances             | 137 |

# LIST OF FIGURES

| Figu | re pa                                                    | ge |

|------|----------------------------------------------------------|----|

| 1.   | Measurement System                                       | 42 |

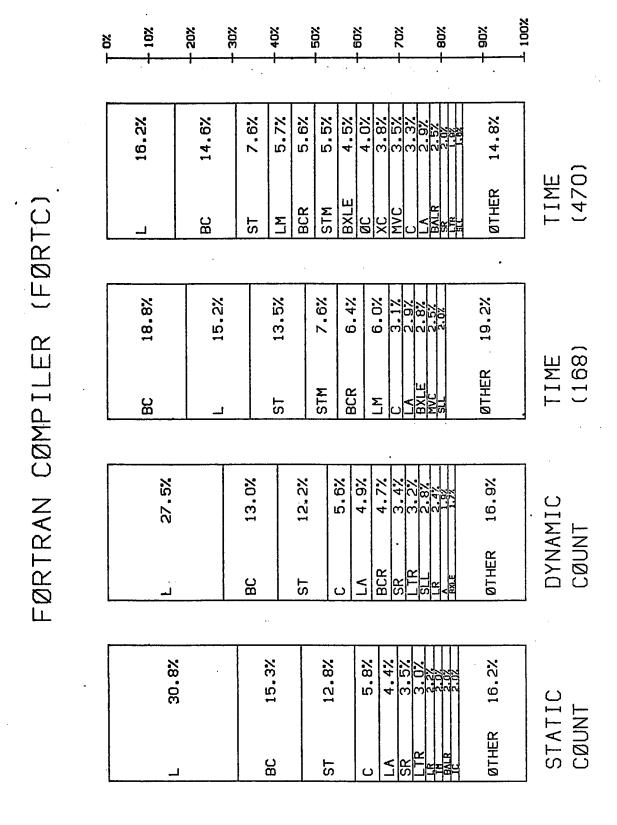

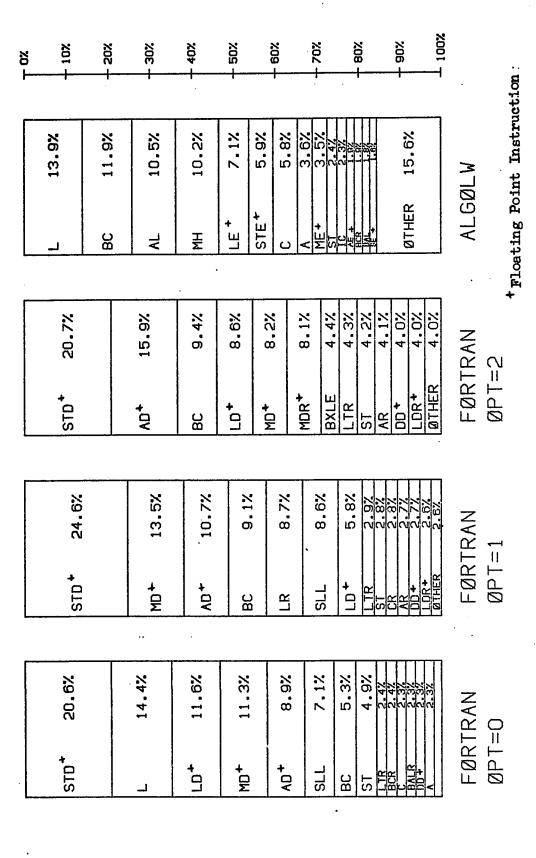

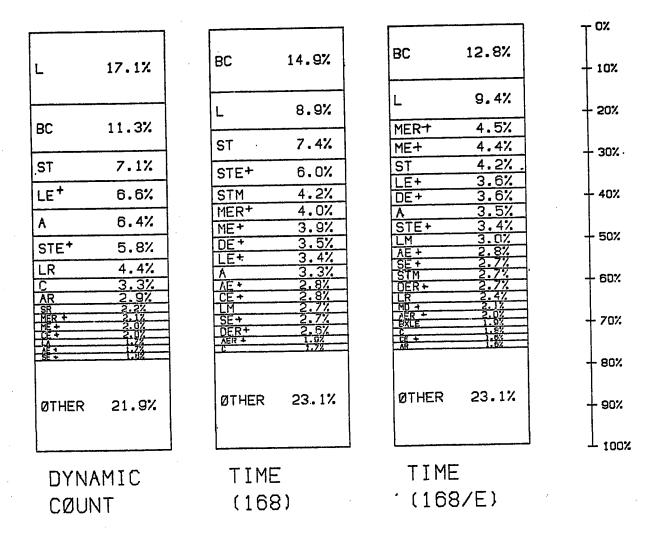

| 2.   | Static/Dynamic Count, and Time by Opcode - FORTC         | 57 |

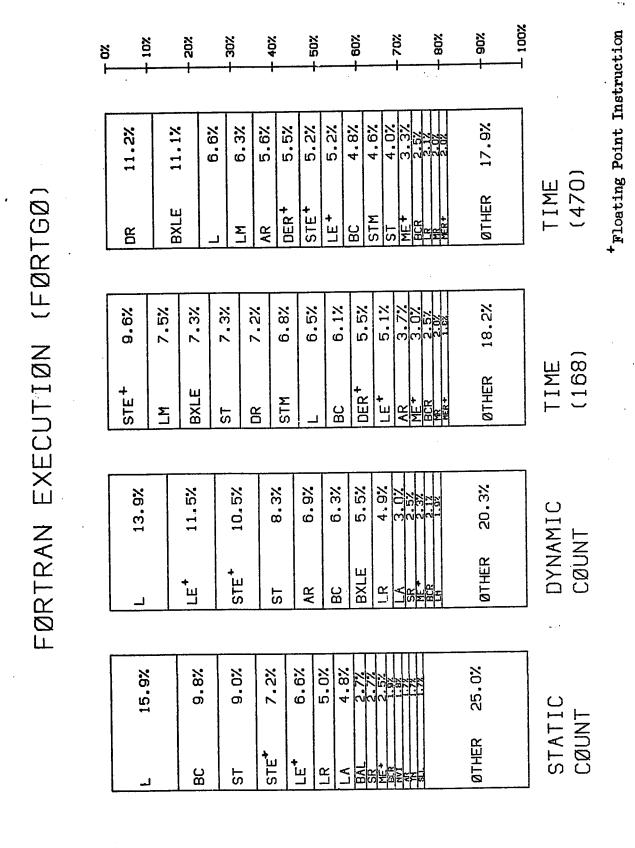

| 3.   | Static/Dynamic Count, and Time by Opcode - FORTGO        | 58 |

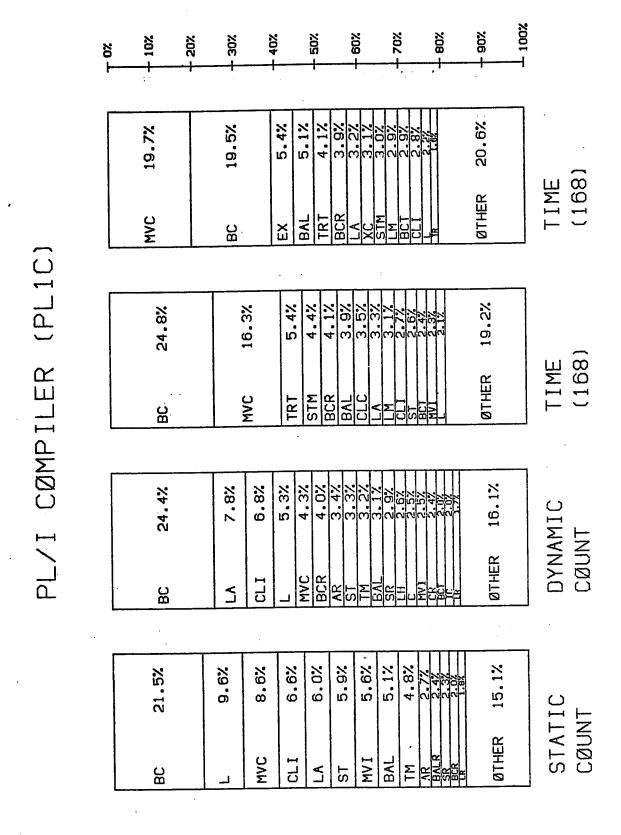

| 4.   | Static/Dynamic Count, and Time by Opcode - PLIC          | 59 |

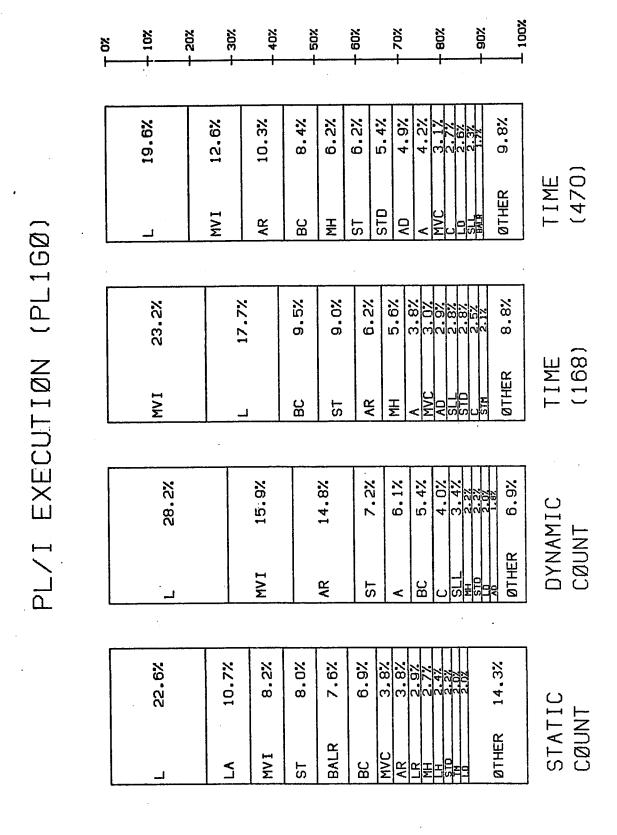

| 5.   | Static/Dynamic Count, and Time by Opcode - PL1GO         | 60 |

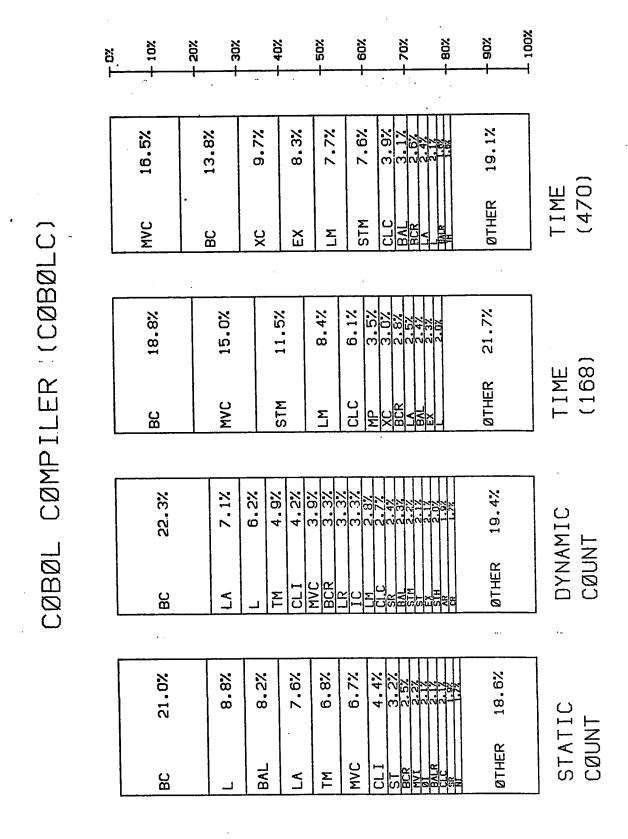

| 6.   | Static/Dynamic Count, and Time by Opcode - COBOLC        | 61 |

| 7.   | Static/Dynamic Count, and Time by Opcode - COBOLGO       | 62 |

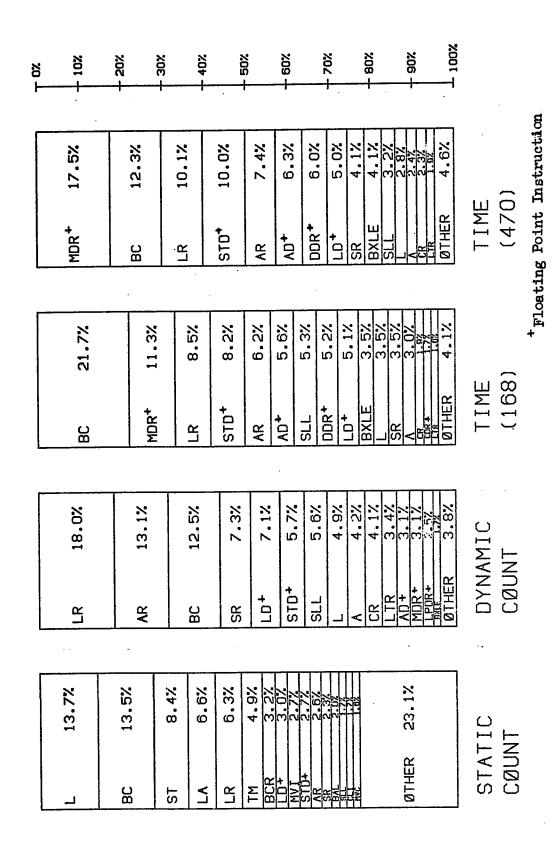

| 8.   | Static/Dynamic Count, and Time by Opcode - LINSY2        | 63 |

| 9.   | Dynamic Opcode Counts - FFT programs                     | 64 |

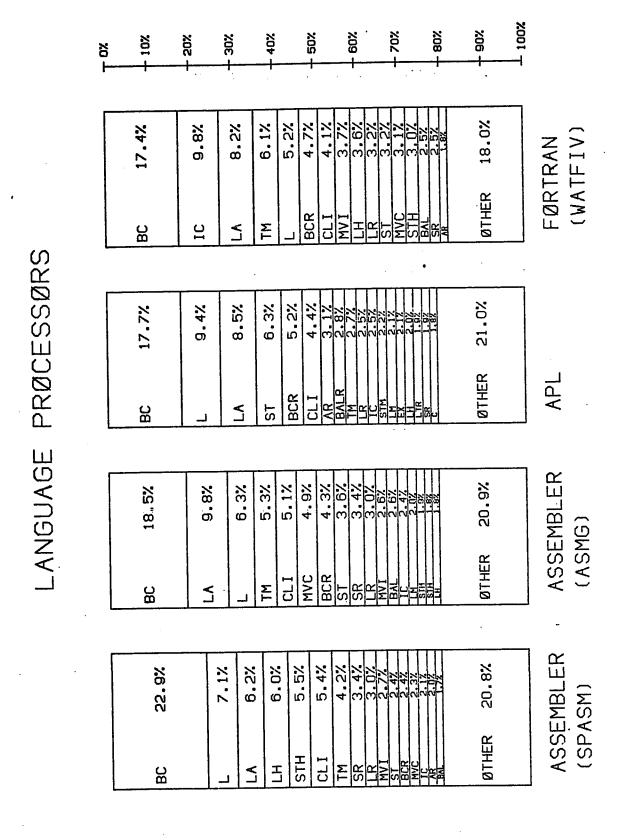

| 10.  | Dynamic Opcode Counts - Language Processors              | 65 |

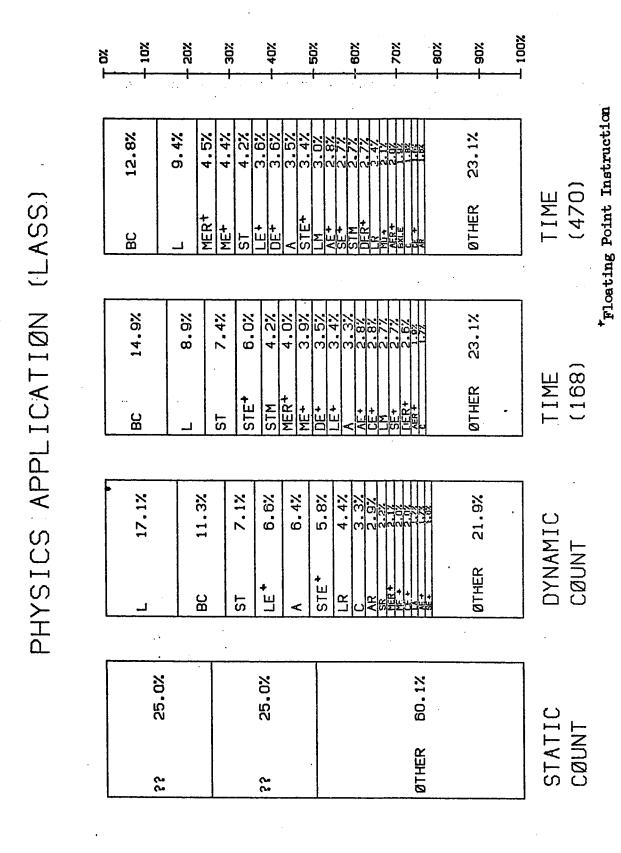

| 11.  | Static/Dynamic Count, and Time by Opcode - LASS          | 66 |

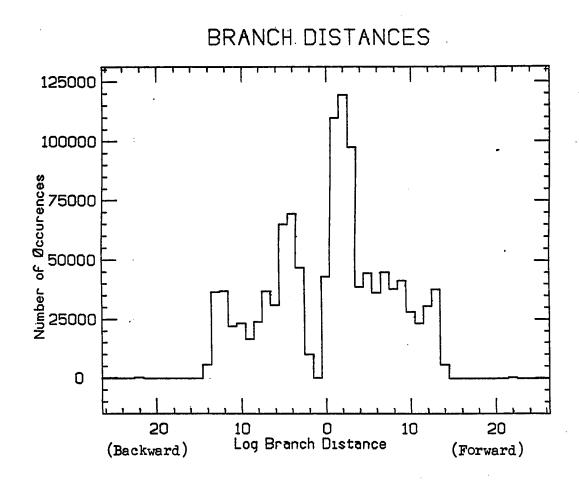

| 12.  | Branch Distances                                         | 72 |

| 13.  | Execution Distance Between Branches                      | 75 |

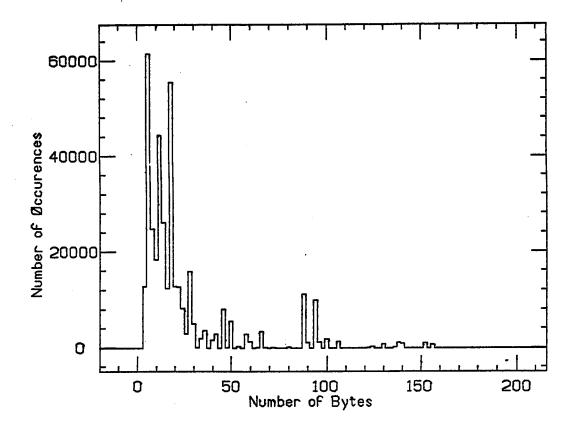

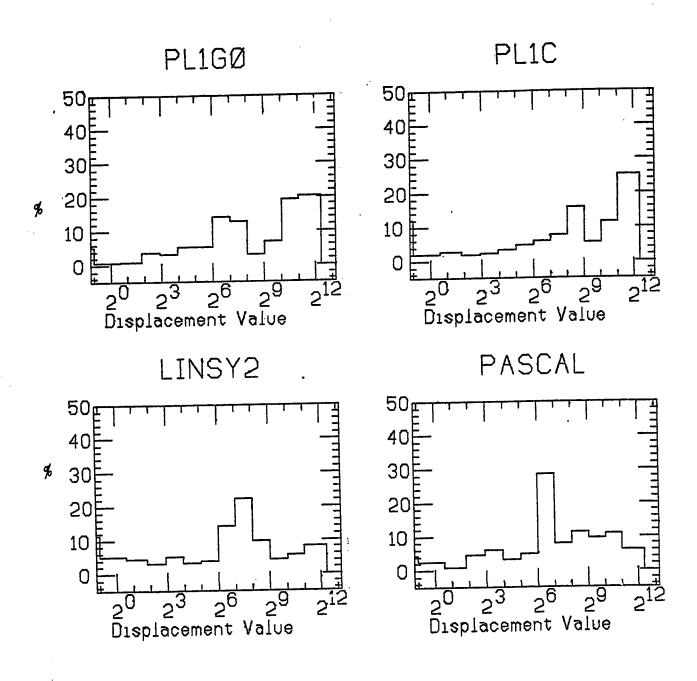

| 14.  | Distribution of Displacement Values                      | 79 |

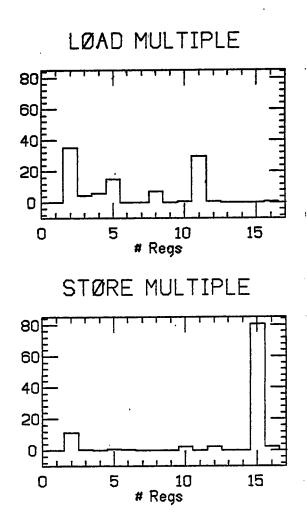

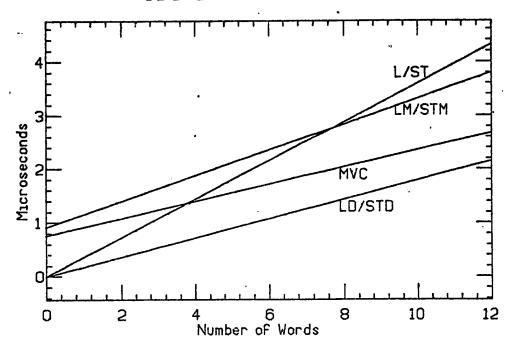

| 15.  | Number of Registers for LM/STM                           | 83 |

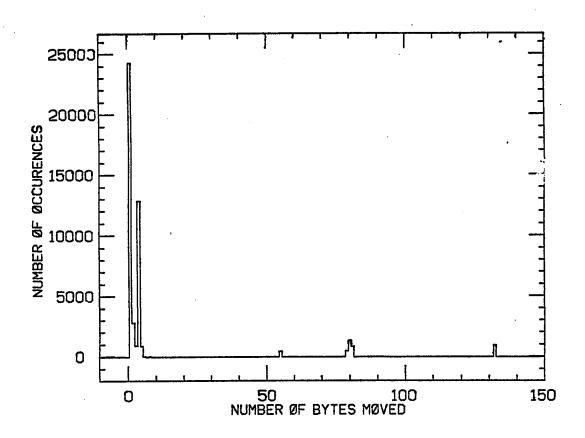

| 16.  | MVC operand length                                       | 85 |

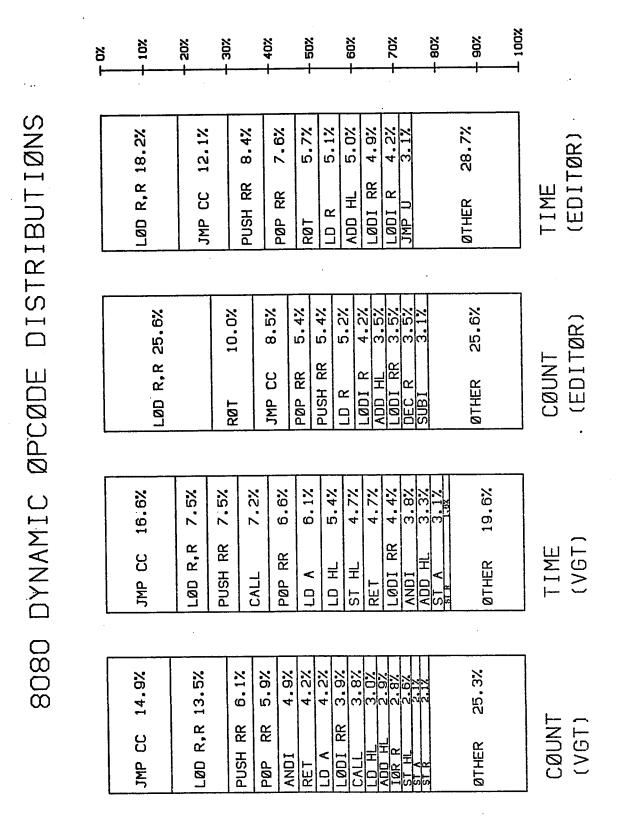

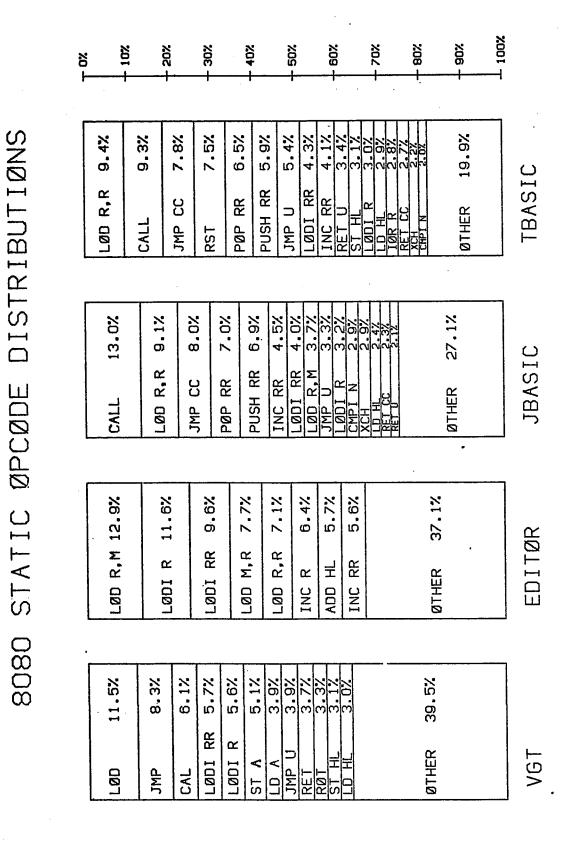

| 17.  | Intel 8080 Dynamic Instruction Count, and Time by Opcode | 96 |

| 18.  | Intel 8080 Static Opcode Distribution                    | 96 |

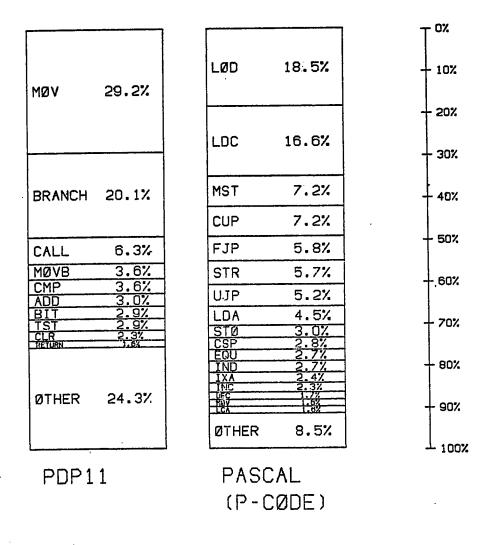

| 19. | PDP11 and Pcode Static Opcode Distributions 106     |

|-----|-----------------------------------------------------|

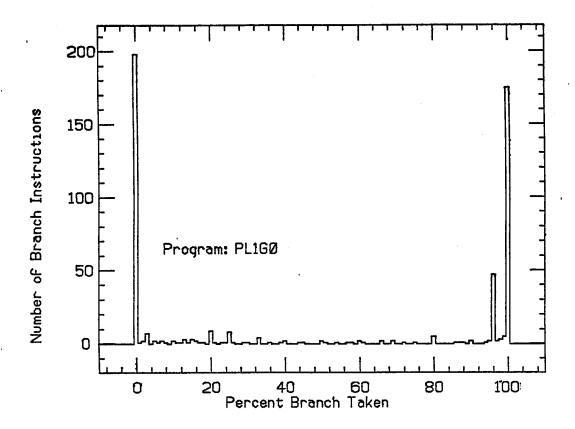

| 20. | Conditional Branch Successes                        |

| 21. | Predicted 168/E Performance Compared to IBM 168 129 |

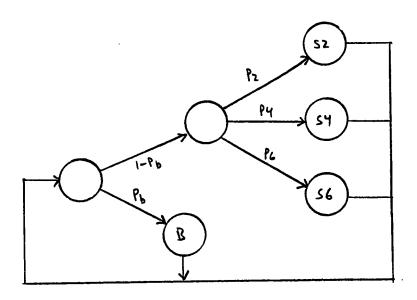

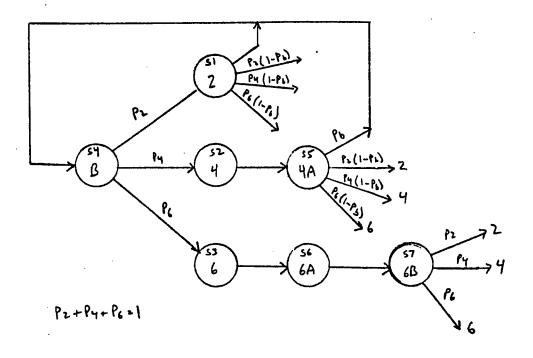

| 22. | Instruction Fetch Model 1                           |

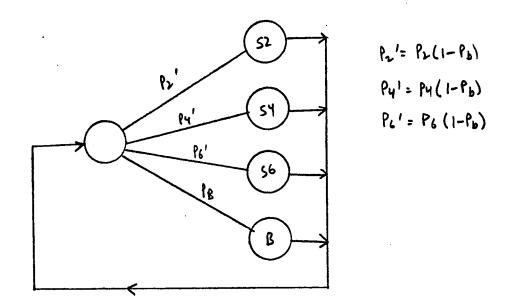

| 23. | Modified Instruction Fetch Model 1 132              |

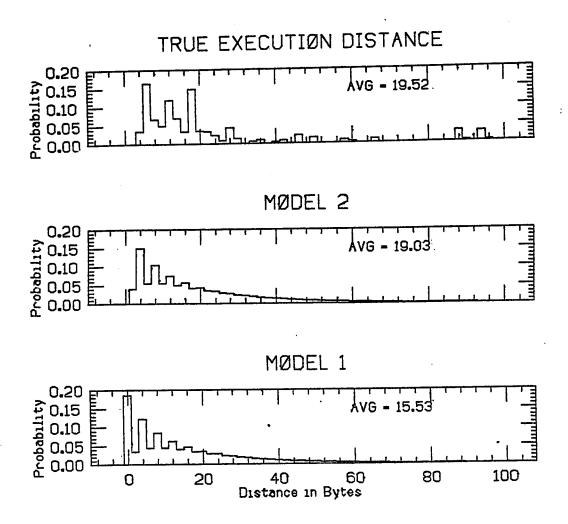

| 24. | Execution Distance Distributions                    |

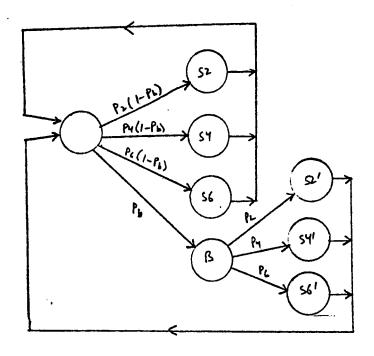

| 25. | Instruction Fetch Model 2                           |

| 26. | Modified Instruction Fetch Model 2                  |

| 27. | Alternate MOVE schemes                              |

|     |                                                     |

### Chapter I

#### INTRODUCTION

### · 1.1 SCOPE

The goal of this study is to examine, understand, and justify some of the many architectural decisions that are involved in the design of a computer. We will concentrate on an analysis of instruction sets, and will, by measurement of the characteristics of their current use, produce conclusions that are useful for future design efforts.

By interpretively tracing programs on a number of existing architectures, a great deal of data is produced which can be used for such architectural studies. The results discussed here can be divided into six types:

- Particular conclusions about the architecture and implementation of the computers studied,

- General conclusions about machine architecture which can be inferred,

- Proposals for improvement which are indicated by these conclusions,

- 4. A set of techniques and tools which are generally applicable to studies of this type,

- 5. The use of these techniques to predict the effect of proposed design changes, and

- 6. A collection of quantitative data which can be used for further study or as a basis of comparison for other architectures.

The techniques will be applied to the extremes of current computers: from high performance implementations of sophisticated processors (the IBM 370/168 and Amdahl 470 V/6), to a comparatively simple LSI microprocessor (the Intel 8080). Particularly for the larger machines, it will be important to demonstrate that the approximation involved in analysis can be verified using the real machines. The true value of these techniques, however, lies in the ability both to predict the effect of changes to particular implementations, and to draw conclusions about the instruction set architectures.

Although a range of architectures is examined, the emphasis is on the characteristics of instruction sets for high performance implementations. As a specific example, the IBM 370 is studied in detail to provide a framework for discussing the conflicting goals of high speed and instruction set complexity.

### 1.2 MOTIVATION

"Errors using even inadequate data are much less than those using no data at all."

-- Charles Babbage (1792-1871)

The design of a modern computer is a complex process that must first begin with an understanding of the general goals, the available resources, and the technological limitations. Even within these constraints, however, the space of possible designs for even modest subparts of the system is extremely large, and hundreds of major decisions must be made before the specification is complete.

This lengthy design process requires that a large number of difficult architectural questions be resolved rather early in the development of the machine. Some of the decisions will have only a small effect on the ultimate performance and others will be crucial, but is it often difficult to distinguish between the two before the development is complete. There are problems of architectural definition which apply to all members of a computer "family" as well as more specific questions that arise during implementation of particular models.

Unfortunately, there is very little information available which can serve as a guide for any of these issues. There is almost no formal theory of computer architecture which is of use to the designer, and there is a

notable lack of retrospective analyses of existing computers in open literature. The result is that the success of the design often depends on the intuition, experience, and good luck of the designers.

The design of the instruction set is an area which can particularly benefit from measurement and analysis of existing computers, especially for architectures which will eventually have high performance implementations. It is important to avoid features for which the commonly occurring cases cannot be easily optimized, yet there are many such examples in popular architectures. In other cases, small changes to the specification of the instruction formats (start/end versus start/length for sequences, for example) can make a large difference in implementation cost yet are almost transparent even to assembly language programmers.

An equally important and perhaps even more fruitful application of such analysis is for the improvement of existing designs. The high cost of software development (and the continuing dependence on machine language programming) dicates that radical changes in machine architecture be made only at infrequent intervals. Although users of a given computer are often willing to expound at length on the deficiencies which seem to them to be the most obvious, it requires careful and precise measurements to identify those areas where efforts to improve the design

will have the greatest effect. It is tempting to concentrate on the defects which most offend aesthetic sensitivities rather than on those whose elimination will do the most to improve performance overall.

Because of the likelihood of later extensions, it is important that the initial design of an instruction set be flexible enough to adapt to such changes. This at the very least requires some unused slots in the encoding scheme, and may also require that some features be left out in order to avoid incompatiblity with likely future additions. The lack of hindsight is a problem, but even later measurements may not be enough to show what the correct decision should have been. It often is easy enough to recognize and measure the effects of mistakes in architecture or implementation, but it is much harder to see what the good features are. Failures are much more obvious than sucesses.

Although it is primarily the computer architecture that is being studied, it is crucial that any such measurements be based on performance while executing typical real programs. The characteristics of a computer system is as much a product of the software which is used as the design of the hardware, and any study which is based only on a theoretical examination of the properties of the design must bear the burden of demonstrating whether it applies to the way the computer is really used.

## 1.3 APPROACH

Any study concerned with the way computers are used must have models for both the computers and the programs which are to run on them. The difference between various models is most often a difference in the level of detail considered; each model makes assumptions about which parameters are significant and which can be neglected.

In queuing theory representations of computer systems, the programs are modeled by their resource request and use characteristics. At this level, the detailed sequence of operations performed by a program are either generated randomly based on known or measured averages (for simulation studies), or are represented by simple mathematical models (where analytic techniques are feasible). This approach has had great success for subsystem-level modeling, where the basic units are memories, processors, and I/O devices. This success is based primarily on the accuracy with which requests to resources can be modeled in a simple, independent fashion.

When the basic units to be studied are at a more detailed level -- registers, cache memory locations, execution pipeline slots -- the queuing model approach fails because no statistically simple model of the resource requests and service can be supplied. The way programs behave at this level is complex, time dependent, and varies

greatly from program to program. For this reason it is best to avoid constructing a model of program activity in favor of using program execution directly to supply the needed data. A convenient way to accomplish this is to use a software interpreter which simulates the execution of a real program exactly as the hardware would but collects, as a side effect, information about that program's use of hardware resources. It is that approach which has been used to collect much of the data used in this study.

# 1.4 USE OF INTERPRETIVE TRACES

A software interpreter has a number of attractive elements which contribute to its usefulness for instruction set analysis and performance evaluation. One of the most important aspects is that a real (non-synthetic) program is executed while the data are collected, so that the resulting evaluation concentrates precisely on the important resources that are used by that program. Put another way, the interpretive technique correctly weights the costs of basic operations with their true frequency of use. We will see later how this can be combined with design information to yield quantitative information that is both specific to particular implementations and applicable to the architecture generally.

The term "implementation" will be used throughout to mean a particular computer design which executes a given instruction set; the design of the instruction set itself will be called the "architecture". Many of the instruction

In addition to hardware-oriented data, an interpreter also provides program-level information that is useful to programmers, compiler-writers, and operating-system builders. The results of particular compiler optimizations, or the cost of certain software conventions can be determined and evaluated. Equally important is the simple satisfaction of curiosity about how the computer is really being stressed. Although the individual instructions were written by the programmers, their aggregate effect (aside from occasionally producing correct results) often comes as a surprise.

An approach often used to gather very similar data is to write (or build!) a detailed simulator of the hardware for a particular architecture implementation. In comparison to this full simulation of the hardware at a detailed level, instruction-level interpretation is relatively easy to do. Although more implementation-specific information can be obtained from a hardware simulator, the high cost of writing and using it has discouraged its casual use. It is generally difficult to modify, expensive to run, and very specific to the particular implementation.

architectures we look at will have several implementations ("models") consituting a family of computers, such as the DEC PDP11 and IBM 370 series. An abstract processor which implements a particular architecture is often called an ISP ("Instruction Set Processor").

Rather than get information which is tightly coupled to the implementation and the hardware, we would like a similar technique which is closer to the architecture and program levels. An instruction interpreter with some knowledge of the implementation is a good compromise that provides a large part of the relevant data at moderate cost.

Much of the information used in this study comes from data produced by an instruction interpreter, augmented by detailed simulation of specific subsystems where necessary. This will be referred to as "dynamic" analysis, that is, analysis of executing programs as seen by the instruction processor, and provides most of the information of interest about performance and resource utilization. In addition, other information will come from "static" analysis of programs before execution; this provides insight into memory requirements (both size and bandwidth), and influences the choice of instruction encoding technques.

#### 1.5 ORGANIZATION OF THE THESIS

The remaining chapters of the thesis are as follows:

Chapter 2 discusses some of the previous work on processor or architecture evaluation, and shows how the work here is related.

Chapter 3 describes the basic instruction timing model used for processor evaluation. The methodology is

explained, and the various factors in the model are examined and evaluated. The model is validated by comparing its prediction to the result of running programs on the real machines.

Chapter 4 is devoted to an analysis of the IBM 370 instruction set architecture. Some of the topics covered are: opcode distributions, instruction lengths, branch analysis, branch and execution distances, opcode pair distribution, displacement values, register use, operand lengths, memory references, and pipeline effects. The discussion includes both architectural points and results related to the specific implementations studied: the IBM 370/168-1 and the Amdahl 470 V/6.

Chapter 5 contains some similar studies of other architectures, but not to the level of detail done for the 370 in Chapter 4. The intent is to complement the 370 analysis by examining those aspects of several other computers that can contribute new information because of their difference from the 370 architecture.

Chapter 6 gives several examples of the way in which the techniques described here can be used for prediction. Examples at three different levels are presented: (1) modification to existing implementations, (2) design of new implementations, and (3) the use of this information in deriving more abstract models of computer and program behavior.

Chapter 7 contains a list of the architectural conclusions which result from this study. The emphasis is on design rules which should be followed to allow instruction sets to be implemented in very high-performance processors. Other observations about the interaction between hardware and software are included.

# Chapter II

#### PREVIOUS WORK

There has been work in at least six areas that is related to the studies described here, or which serve to supply a perspective from which to view this work. Those areas are:

- 1. System-level performance evaluation

- 2. Benchmarking for processor evaluation

- 3. Modeling for processor evaluation (both analytic and simulation)

- 4. Measurement of language characteristics

- 5. Instruction timing studies

- 6. Measurement and evaluation of instruction types

The common thrust of these fields is an evaluation of the ultimate performance of a computer system; each approaches it from a different level or with different techniques.

# 2.1 SYSTEM-LEVEL PERFORMANCE EVALUATION

From the user's point of view, the performance of a computer system is a composite of the performance of the hardware, the system software, the language processors, and the application programs. The most difficult part of improving such a system is often simply identifying the bottlenecks for which modest additional work could achieve dramatic changes. A substantial literature exists which describes available techniques and examples of system performance evaluation; a recent bibliography appears in [AGA75].

Since the analysis of the total system is such a complicated affair, purchasers must rely on benchmark runs for comparative evaluation of competing systems. While this for determining the overall is an adequate technique performance of a complete computer system, it gives little useful insight about the individual components. encourages the attitude which blames all performance difficulties on the instruction-execution hardware because it is the obvious base. It is often much easier to performance by spending a few extra million dollars on a faster CPU than by considering alternative operating systems, languages, or problem-solving techniques. The work related to the most concerned with is are here performance of the instruction-execution part of the CPU, but this emphasis should not be taken to indicate that the other aspects of total system performance are not significant.

# 2.2 BENCHMARKING FOR PROCESSOR EVALUATION

Benchmarking has always been used to compare computers, such attempts result in but almost all a composite comparison of processor, I/O devices, operating system, and applications software. Some benchmark studies have been made to compare specific machines, but only when the architecture and software is the same for both is the comparison easy to interpret. Examples of this type are Amdahl 470V/6 IBM 370/195 [SNI76] and the same Amdahl to the to IBM 370/168 [EME75]. These studies, however, are concerned only with performance analysis for the user's benefit; one of the goals of this dissertation is to extend that analysis so that it is useful to the computer designer.

There has been some systematic work done to use benchmark programs for the evaluation of a variety of processors. Wichmann, for example, has used machine-independent languages to measure processing speed; in [WIC73] the time taken to execute 42 different basic statements in ALGOL 60 was measured on some 50 machines. By assuming that the time Tij for a statement i on machine j can be factored as Tij=Si\*Mi, where Si depends only on the statement and Mj depends only on the machine, then a least-squares fitting process yields the Mj as comparative measures of machine performance.

One of the major difficulties with such an approach is that it is very sensitive to the quality of the compiler on the different machines. The IBM machines, for example, were at a disadvantage because the only commercially available ALGOL compiler (ALGOL-F) known to produce rather inefficient code. Another problem is that the statements were not chosen or weighted to account for the unequal frequency of use in typical In an attempt to overcome these difficulties, Curnow and Wichmann [CUR] developed a "synthetic benchmark" which has the following properties: (1) The program was made to match, as closely as possible, the same distribution of intermediate Whetstone code [RAN] as was produced by 949 programs previously collected and analyzed [WIC70]. (2) The program had to be translatable into a variety of languages (ALGOL, FORTRAN, PL/I) (3) No constructions should be used which would give a particular language or compiler an obvious advantage. For example, they attempted to "ensure that the program could not be logically optimised" so that statements would not be removed from loops by compilers clever enough to detect when it would be possible. That this had been achieved was verified by examining the object code produced.

The ranking of 10 different machines was compared using the results of the synthetic benchmark in different languages, and also compared to the ranking obtained by a

Gibson Mix (see section 2.5) and the original ALGOL statement mix. The result was that despite the care taken to avoid the influence of compiler differences, the effect of the language often made the machine differences insignificant. Two computers with one twice as fast as the other in a FORTRAN comparison could be the same when compared with the ALGOL versions of the program. The conclusion may well be that it is impossible to make language— and compiler—independent performance comparisons of machines with different architectures without simultaneously comparing the language and compilers. The study of a computer as an Algol machine, while useful for some purposes, tells little or nothing about the instruction—set processor beneath it.

### 2.3 PROCESSOR MODELING

Although a model of a CPU is a model of an instruction set processor, such models provide little insight into the design of the instruction set. The work in processor modeling has been mostly concerned with the internal organization of the computer, and not with representation at the level of the instruction set and the relationship to programs.

The elements of the models are the physical structures of a particular implementation — the instruction fetch mechanism, the arithmetic units, the pipeline controls, etc.

The models (and the element characteristics) are sometimes simple enough to be approached analytically, but discrete simulation is more often necessary. Such studies are valuable both for understanding existing processor implemenations ([NEW] is a simulation example applied to the PDP10), and for the analysis of proposed new structures ([BOW] is an example of an analytic model for multiple function—unit processors). Such modeling has not been appropriate for the analysis of instruction sets, however, since the emphasis is on the structure of the implementation and not the consequences of instruction set design.

# 2.4 MEASUREMENT OF LANGUAGE CHARACTERISTICS

One way to approach computer architecture is to begin with a study of the languages to be used. By determining what the common constructions are, one might then be able to design appropriate machine language primitives for efficient execution. Language studies could also be used to evaluate existing machines by examining the extent to which the frequent basic operations can be translated to efficient machine code.

Such studies have been made for several languages; among them are FORTRAN [KNU,LYO,SLA], PL/I [ELS76a,ELS76b], COBOL [SAL], ALGOL [BAT], XPL [ALE72,ALE75], and APL [SAA75]. Most of the results are concerned with the frequency of use of various source-language constructs, and

many of the results are surprising. For example arithmetic expressions, whose code optimization has received a great deal of attention, are almost always trivial; Knuth's FORTRAN study [KNU] found that 68% of all assignment statements were replacements of the form A=B, and that the average number of operands for all expressions was only 2! Such information is clearly important both for the design of languages but especially for the design of compilers.

as these studies are for language research, Useful little light is shed on the problem of matching the language to the hardware which supports it. Much of the work on the interface concentrates on compiler optimization rather than instruction set optimization. Among the few notable exceptions are the theses by Wortman [WOR72] and Hehner [HEH74]. Even there, however, the emphasis is almost entirely on the use of clever encoding techniques to reduce memory use, and therefore based the designs are on static statistics. The result, in Hehner for example, is a 75% decrease in space compared to conventional machines, but at the cost of "an increase in hardware complexity" whose effect on performance is not considered.

## 2.5 MEASUREMENT AND EVALUATION OF INSTRUCTION SETS

A great deal of the literature on the evaluation of instruction sets is concerned with frequency of execution counts. The seminal work was an unpublished study in the

late 1950's by Gibson, which presented the result of measurements for the then popular IBM 7090. (The Gibson study was finally distributed a decade later as an IBM Technical Report [GIB].) In addition to instruction frequencies obtained by tracing program execution, Gibson defined 14 different basic instruction classes and their fractional use; this "Gibson Mix" has come to be used as the representation of a "standard load" for an instruction processor.

By classifying an arbitrary instruction set according to Gibson's categories, and using an average execution time for each class, the resulting instruction execution rate can be used to compare different computers. The difficulty with this approach, of course, is a consequence of its simplicity. Many instructions are hard to classify into the original categories, and variations in execution time due to address modification, operand variations, and data dependences are difficult to assess. In fact, reliable timing information for any of the high-performance computers is complex to interpret if it is even available at all. Nevertheless, some systematic uses of Gibson-like mixes have been useful in obtaining crude rankings of various dissimilar computers, especially when the mix results are presented along with results of benchmark tests, as they are in the NPL data base of computer performance information [VER]. Specialized mixes can be of use if a particular application is involved; computer evaluation by the U.S. Army [WOL] concentrated on the solution of differential equations and developed a mix based on an analysis of the algorithms used.

A variety of data has been published for several machines since the years of the Gibson study, and many have extended the information collected to include opcode pairs, register utilization, and static vs dynamic frequency comparisons [LUN, FLY, WIN, HAN, AGA73, ANA, FOS71a,b, SAA72, ROE]. Most of these studies are unfortunately rather small in scale, due to the high cost of the data collection. In addition, little timing or performance information is provided, and no analysis of the effect of instruction-set design and use on the implementation of processors is done.

Most of the instruction-set analysis as a result of measurement has concentrated, as have the language-oriented instruction set analyis, on efficient encoding of instructions [FOS7la, HEH76, HEH77, WIL]. Although there is certainly some relationship between instruction encoding and performance, it is becoming less significant as a result of techniques such as instruction caches, pipelines, and the general increase in memory bandwidth and capacity.

A more recent systematic comparison of instruction sets has been done as part of the Computer Family Architecture study for miliary computers [FUL]. Three quantitative measures of instructions were defined: the S-measure for the

static space taken by the program, the M-measure for the amount of memory traffic generated, and the R-measure for the amount of internal processor computation required. Test programs coded for several machines were traced so that the S, M, and R measures could be determined, and a variety of programmers and programs were used so that the differences due only to the instruction set could be statistically isolated.

This approach is probably the best to date for comparing architectures independent of implementations, but to extend its use it is difficult to issues of It may be possible to demonstrate a cost/performance. correspondence between the quantitative measures processor complexity or speed, but that work remains to be done. There are other issues with regard to the choice of test programs and the effect of higher-level languages (all test programs were in assembly language) that need to be studied further. The more important issues instruction types should be included at all, and what the tradeoffs are between instruction set complexity, programming ease, and processor performance have not been addressed by any of the measurement-based studies.

## 2.6 INSTRUCTION TIMING STUDIES

information for instructions and Accurate timing unusual conditions is required in order to be able to evaluate a processor at the instruction execution level. That information is hard to get, and the major difficulty is the lack of published data from the manufacturers, particular for the high-performance machines. There is a distressing trend toward providing as little information as The excuse is often that the the buyer will tolerate. information is complex and difficult to present, but given the examples set by some [AMD] one cannot help but conclude that information is often withheld because it is a potential source of embarrassment. Some expurgated papers reveal glimpses of large-scale efforts with sophisticated tools [VAN, HUG, MUR], but few of the results are ever presented publicly.

This situation has forced users into the position of empirically measuring the machine characteristics; notable examples are for the CDC 7600 [LIP, MAR], and the IBM 370/168 [EME]. None of these are concerned with the relationship between the design of the instruction set and the ultimate machine performance, but they supply useful data.

The methodology involved in doing accurate timing studies for high-speed computers in real environments is complex, and some other experiences in this field were useful in developing the techniques we used [WOR76, GEN].

### Chapter III

#### INSTRUCTION TIMING MODEL FOR MACHINE EVALUATION

One of the most important tasks for a computer designer is the evaluation of a computer architecture implementation. As a specific instance of that task, this chapter compares the implementation and performance of the IBM 370/168-1 and the AMDAHL 470 V/6, which are two high-performance machines with the same architecture [IBM70] but different implementations.

This chapter explains, in detail and by example, the methodology used for the analysis of instruction sets. It discusses the model based on instruction timing, the process of evaluating important factors, the tools needed for such a study, and the verfication procedure. Although presented in the context of the IBM 370, the approach is a general one. Results in detail for the 370 architecture and similar results for other architectures appear in subsequent chapters.

## 3.1 THE MODEL

The basic goal of the measurement system is to apportion the time spent by an executing program among the various system components such as the cache memory, the instruction pipeline and the individual instructions, so that resource utilization and system bottlenecks can be determined. This is achieved by using simple models of the CPU of each machine which also provide estimates of the total CPU times. The total time is important insofar as it is used to verify the accuracy of the model, since the predicted times can then be compared to the actual performance of the machines.

The decision to make implementation dependent measures of CPU performance for two members of a specific architecture family has several advantages:

- Some of the traditionally difficult problems encountered when comparing two different architectures are not present, since many confounding factors relating to performance evaluation have the same effect on both machines.

- 2. The success of one of the levels of a complex system can often be measured by the characteristics of the levels below. Performance evaluation which is close to the implementation level of a computer gives valuable design information at the architecture level.

- 3. The speed of collection and the precision of the results are greatly enhanced by having tools that are tailored for a specific instruction set.

- 4. Practical and useful results can be obtained quickly, so that those results can be used to further refine the tools.

### 3.1.1 The Technique

The models of the CPUs used here are based on the instruction timing formulas available from the manufacturers' documents which describe their computers These documents sometimes sacrifice details [AMD, IBM74]. for ease of exposition (which is not to say that they are easy to read!) and represent only the best efforts of an engineer to describe the existing machine. Efforts which are described later were made to verify the accuracy of the information. In deriving the model for the Amdahl machine we were quite fortunate to get some help from the designers.

The programs to be measured were traced in user state, and all the information required to compute the instruction execution time from the formulas was collected. A record was made of counts of occurrences, values of instruction variables used in the formulas, and information about memory performance. Typical variables depend on the specific instruction but may also depend on the implementation

details. For example, the number of bytes moved is implementation independent, but measures of pipeline interlocks and timing delays are not. Some variables depend on instruction environment and therefore require information about instruction pair and triple distributions.

Two primary constraints caused us to trace only userstate instructions. (1) Tracing system software, with the

attendant performance degradation of at least 50 to 1, would

modify operating system behavior in timing dependent I/O

sections. By tracing only in user mode, which is usually

not speed dependent, we eliminate a source of error which

would necessitate a complicated interpretation of the

results. (2) Tracing the operating system introduces a

large number of problems involving the recording of the

trace data. One standard solution is the use of samples

rather than complete traces, but then the verification of

the predicted CPU time is not possible.

Since the timing formulas do not include the effects of cache memory misses, the cache memory is simulated for each machine. The cache miss penalty is added to the instruction execution time to obtain the expected program execution time. To verify the model the expected time is compared to the operating system accounting time corrected to compensate for the differences between the measurement methods.

The effects of instruction interaction, which can generally be attributed to pipeline resource interlocks, are rather explicitly accounted for in the Amdahl formulas. For IBM, however, the pipeline effects have been averaged into the formulas in a way which was not clearly indicated. This was a potential source of difficulty, but the effort required to obtain this information from the logic diagrams and microcode listings was prohibitive, and unjustified when an error of a few percent is acceptable.

The techniques used here are much more complex than benchmarking, but not as costly as total hardware simulation. The tools are general enough so they can be — and have been — used for other studies with different objectives. The importance, however, lies in the ability to change the model variables to reflect proposed changes to the existing hardware and to accurately predict the performance effects of those changes.

### 3.1.2 Evaluation of Important Factors

The development of the CPU model has been greatly influenced by the idea of an evolving system of tools—development by successive refinement. A crude model and simple tools were first assembled and by successive iteration new tools, new measurements, and a more refined model were designed. This approach reduces the number of false starts and the elapsed time of the whole study by

quickly allowing the effort to concentrate on the most important factors.

The CPU model used is an intermediate one between full simulation at the hardware register level and a machine-in-dependent representation of performance. The decision to include some factors and exclude others was based on an estimate, often supported by experimentation, of the effect of those factors on the final results. Some of the justification for the decisions are presented below.

The accuracy of the model is supported by the match between the program execution time as predicted by the model and the same time measured by the operating system during actual runs. Performance evaluation by benchmarking is repeatable only within 2-3% because of the large number of uncontrollable variables, and this therefore puts an upper bound on the precision of the validation.

An examination of previously published instruction frequencies might suggest that the more frequent instructions are those whose duration is constant and therefore do not heavily depend on execution variables like the length of operands. If this were true, then those variables could be set to program-independent values without introducing a significant error in the result. To test this hypothesis, the program which computes execution times was given three sets of execution variables with which to predict program

running time. One was a programmer's best guess of the true values, and the other two were the smallest and largest extremes which could realistically be expected. The results showed that an instruction could jump from 4% to 50% of the total time depending on the value of its variables with all others remaining the same. This is an unacceptable error, especially since errors in the variables for many instructions could combine to form large systematic errors. Most of the variables which affect execution time were therefore measured exactly or estimated from related measurements.

The predicted execution time is composed of the aggregate instruction timing results and a penalty for cache memory misses. The aggregate instruction timing results have already taken into account the instruction counts and basic execution speed, as well as the pipeline interlocks. The cache miss penalty depends on the reference pattern of the program, the cache organization, and the data flow pattern within the machine. The two machines differ rather markedly in those respects: the 370/168 uses aligned doubleword (8-byte) accesses and an associative set size of 8, while the 470 accesses unaligned fullwords (4-bytes), uses a set size of 2, but has the same total amount of data (16K bytes). Both caches use an LRU algorithm to determine which 32-byte line within a set is replaced when new data is to be fetched 1. There are also significant differences in

the amount and type of instruction lookahead performed. To accurately measure the cache penalty, the trace analysis program has a detailed simulation of the cache and instruction fetch mechanism of both machines.

Although cache memory miss ratios are known to be low [MER], it is easily shown that the contribution of the time penalty for the misses is too large to be neglected. If the miss ratio is 5%, with a 480 nsec penalty for a miss, 1.6 memory requests per instruction, and an average instruction execution time of 300 nsec (reasonable values for the 370/168) then the cache misses represent a 13% increase in the execution time.

Two other cache organization features must be considered in the cache penalty correction. For IBM, stores always access main memory ("store-through") which may cause extra delays. For Amdahl, there is an extra penalty when a 4-byte access crosses a cache line boundary. These and the other cache corrections are not attributed to the instructions which caused them, but rather accumulated separately.

Although the 168 set size is 8, the LRU algorithm treats each pair of two lines as a group and the least recently used group is replaced. This is "worse" than a true 8-way LRU algorithm since very old data may be paired with new data in a group and never be replaced, but the cache was originally designed for 8K and was expanded with minimal hardware additions.

The measurement of user-state instructions in a production operating system environment caused some difficulty in determining the true CPU time. The execution time reported by the operating system includes all user-state and some supervisor-state instructions [BEN], whereas the trace program measures only user-state instructions. The time attributed to these supervisor-state instructions executed in the processing of user-initiated supervisor calls (SVCs) must therefore be subtracted from the reported CPU time. Measurements were made of the charged time for all the relevant SVCs as the programs were traced. The correction is very significant for almost all programs, since both the number and cost of the SVCs are high. For the 168, for example, the time charged varies from 107 usec for an I/O operation to 26 msec for opening a file.

Although the SVC time correction could have been measured for the original benchmark programs, they were somewhat modified in view of the substantial correction required (as much as 20%). Wherever possible, the number of I/O operations was reduced by increasing the file blocking factors, but the operation of the programs was not otherwise altered. Despite this effort, the SVC time correction remained the factor which introduced the largest error in the measurements. We also traced a FORTRAN numerical analysis program from which the I/O parts were excised, so that few supervisor services were requested.

Since supervisor-state and user-state instructions share the same cache, there will be some displacement of the user's "working set" from the cache in response to an SVC, which will manifest itself as a lower than normal hit ratio when the user's program is resumed. An unpublished note by Rossman suggested that this would have a large effect [ROS]. To verify this the cache activity for one job with a large number of SVCs was simulated -- first assuming a 100% cache flush for each SVC, and then again with no flush. number of cache misses changed by a factor of 10. Measurements showed that the actual fraction of the cache displaced by the various SVCs varies from  $\emptyset.16$  to 1.0, and that almost all non-trivial requests completely replace the cache. cache simulator therefore took this into account by flushing fraction of least-recently-used cache the appropriate entries when an SVC was executed.

Interrupts which occur during the execution of the program do not account for a significant increase in accounted time (since the user-state CPU timer is disabled during interrupt processing) but there could be an effect due to cache displacement caused by the interrupt routine. On a heavily loaded machine interrupt rates as high as 4000 per minute are common, representing at worst 16.4 ms of extra time (1.7% for IBM) to completely refill the cache for each second of CPU time. Since most of those interrupts are due to other jobs, this effect was reduced to a negligible

level by running the job on on otherwise idle system, so that only the few interrupts caused by the benchmark job itself could cause interference. This is unlike the SVC correction, for which no change in the number of cache flushes is possible simply by controlling the environment of the benchmark run. Similar calculations for the effect of channel I/O transfers to memory show that they have even less effect on CPU performance. This is true both for IBM, where the channels transfer directly to main memory and invalidate corresponding cache entries, and for Amdahl, where the channels transfer into the cache.

## 3.1.3 <u>Instruction Timing Formulas</u>

An instruction may have several timing formulas associated with it, corresponding to different modes of execution. Each individual timing formula may depend linearly on the variables (the most common case) or have a more complicated dependence. In general, three types of linear formulas are encountered.

Some timing formulas reduce to a constant, and often only one formula is associated with an instruction. Examples of this case are most register-to-register arithmetic or logical instructions.

ADD REGISTER IBM .080 usec (AR) Amdahl .065 usec

Many formulas have a simple linear dependency on execution variables. An example is a Load Multiple (LM) instruction which can be expressed as

Load Multiple IBM .520+.080\*R usec (LM) Amdahl .065+.065\*R usec

where R is the number of registers loaded.

some formulas may involve variables which are concerned with the general environment of the instruction. These are often measures of the effect of pipeline interference which causes a delay in the execution of an instruction. Examples are the Amdahl variables Sl and DWD. Sl accounts for some cases of pipeline interlocks, and ranges from Ø to .065 usec depending on the "number of execution cycles attributable to the three words of the instruction stream following the instruction of interest" [AMD]. DWD, which is either Ø or .0325 usec, compensates for the occurrence of a doubleword result instruction before the subject instruction, because the machine is fundamentally single word oriented.

Store (ST) Amdahl .065+S1+DWD

When several formulas are associated with one instruction, each formula applies only to a specific case of its execution. For example, the Move Character instruction execution formulas depend in important ways on the degree of overlap of the two operands. The different cases involve not only different coefficients, but often different variables.

IBM .760+.040\*B usec (no overlap) Move (any 'overlap) Character .640+.240\*B usec (MVC)

Amdahl .195+S1+.130\*WB+MV usec

where MV = .130\*W(no overlap, or overlap>32 bytes) (3<overlap<=32 bytes) MV = .1625\*W(1<overlap<=3 bytes)</pre> MV = .130\*B

MV = .195\*B(overlap=1 byte)

B = number of bytes moved and where W = number of words moved

WB = number of bytes which must be moved to have the destination field on a word boundary when B>63.

For all the individual linear formulas, only the counts and average variable values for each of the timing formula cases need to be accumulated.

Unfortunately, some formulas are not linear in their variables. Typical examples are the decimal arithmetic instructions, where the duration depends on the product of the lengths or the average value of the digits used. For these the appropriate products of variables are accumulated at the time the program is analyzed, and these values are averaged for use by the other programs in an equivalent linear form. These cases of non-linear formulas are sufficiently infrequent to justify this special treatment, but the effect on timing values is too important to ignore them. A simpler approach would assume that the product of the averages is a sufficient estimate of the average product, but the potential error is great.

Divide IBM 2.42+.60\*(N1-N2)\*N2 Decimal (DP) Amdahl 20+(5+4\*Q)\*(N1-N2)+2\*RW if N2<=3 Amdahl 27+(9+6\*Q)\*(N1-N2)+2\*RW if N2>d3

where N1 = length of first operand

N2 = length of second operand

Q = 1 + average value of the quotient

digits

RW = number of fullwords in the result

The formulas are encoded as a string of records, each corresponding to the coefficient of a term in a subcase of a timing formula for a particular instruction; there are a total of 3200 variable names and coefficient values. A numbering and naming scheme was devised that allows variables which are common to many formulas to be propagated to all appropriate places, as well as giving individual identities to variables which are used more restrictively.

### 3.1.4 Measurement Approximations

Some of the variables required for the computation of the instruction times are difficult to measure; this is especially true for those which involve interactions of sequences of intructions. An approximation technique was used for the computation whenever it could be shown that it would not significantly degrade the accuracy of the result.

As an example of this approximation technique, consider the interlock variables called S1, S2, and S3 for the 470, which represent time penalties added to an instruction

because the instructions which follow do not have enough execution cycles to "hide" the completion of the subject instruction. The time penalty caused by these pipeline "breaks" depends on a particular sequence of instruction types, but can be more simply described as an addition to the execution time of particular instructions whenever they are in certain environments. For the Sn interlocks, the definitions are:

where M is the number of execution cycles attributable to the three words of the instruction stream following the subject instruction, and

where P is the number of execution cycles attributable to the two words of the instruction stream following the instruction of interest.

In order to avoid computing the frequency of occurence of all 7-tuples of instructions (at most 6 instructions can follow the subject instruction in the three words which follow), a set of instruction classes was defined where each class contains instructions of the same size and approximately the same execution time. It is then computationally

feasible to accumulate the occurence of relatively long sequences of classes and use these to estimate the true value of the variables. For each instruction which incurs any of the Sn penalties, all possible sequences of subsequent classes are examined. For each sequence, classes are examined until the sum of the instruction lengths exceeds three words (for S1) or two words (for S2 and S3). The sum of the average execution time of the instructions of each class in the sequence is then used as the value of M (for S1) or P (for S2 and S3). Each possible sequence is weighted by its probability, estimated by the frequency of occurence.

The characteristics of the 10 classes were chosen to minimize the error in the computation. All instructions with the same length which have execution times greater than 6 cycles are put in the same class, since the occurence of any instruction of this type in the sequence will automatically force the interlock parameter to be zero. The other classes make much finer distinctions between instructions with small execution time, since they have the potential of making a whole cycle difference in the final value.

Note that the class assignment depends on the estimated execution time, which in turn depends (because of the values of the interlock variables) on the class assignments. Initial class assignments were based on rough estimates of

execution time using what seemed to be reasonable guesses for interlock variables. The class assignments were refined as a result of getting more accurate execution times but the differences were negligible because the averaged value of the interlock variables is so small that it has a very weak effect on execution times and hence made almost no difference in class assignments.

### 3.1.5 <u>Description of the Measurement System</u>

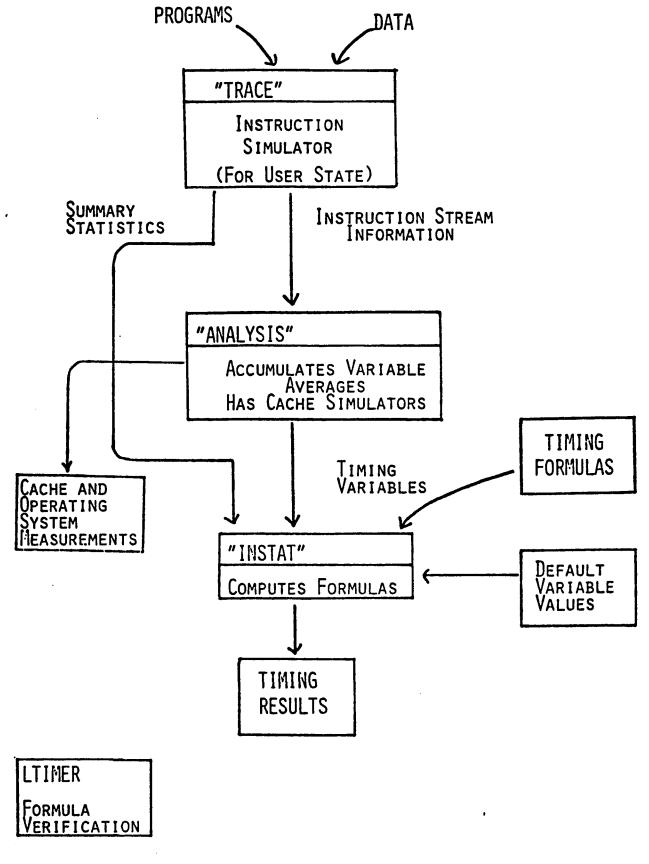

The heart of the measurement system is an interpretive trace program (TRACE) which executes arbitrary load modules (relocatable program files) containing user-mode instructions. Programs are interpreted with precisely the same environment that would be experienced without the tracer; the real data files are used, the same supervisor services are requested, and the same results are produced. As a side effect, however, instruction trace records are produced which can be used to form a detailed characterization of the program. Other trace records are produced which contain information relevant to the tracing process, or to program activities such as exception interrupts.

The record produced by the interpreter for each instruction contains the instruction type, memory addresses referenced, and the other required information. These records are processed by a trace analysis program (ANALYSIS) which generates instruction counts, variable values, and

memory access statistics such as cache memory miss counts, which are stored in a summary file. In order to avoid saving massive amounts of intermediate trace information (25 megabytes per traced second), the TRACE and ANALYSIS programs may execute as coroutines. The combined overhead of the trace and trace analysis programs amounts to 300 seconds per second of real time. This compares favorably to other more detailed hardware simulations, where the overhead has been as high as 6000 seconds per second of real time [VAN].

The summary file is converted into a count file by an intermediate program (CONVERT). The count file contains all the information required to compute the timing formulas for both machines (the 168 and the 470) condensed into about 600 numbers. An instruction statistics program (INSTAT) uses the count file and files of encoded instruction timing formulas to produce the timing and performance information.

Several test programs were devised for verifying the formulas and understanding the measurement factors. A general instruction timing program (LTIMER) was designed for precise measurements of instruction times, cache memory miss penalties, SVC times, and the effects of SVCs on cache memory contents. Each instruction, instruction sequence, or memory access pattern can be executed in a variety of environments so that a systematic study of the variations in execution time can be made.

The measurement system therefore consists of a number of independent programs which communicate through well-defined interfaces, as shown in Figure 1. Each of the interfaces is general enough so that other programs could have been used -- and in fact at various times were used -- for other types of processing. A number of address traces for other cache and virtual memory simulations have been produced [RAF,SMI,YU]. We could have merged some of the processing programs, but in doing so would have lost some By requiring that generality we guaranteed, for example, that neither the trace program nor the trace analysis program knows anything about the details of the timing formulas. In fact, only CONVERT has specific knowledge of them; INSTAT knows only about the timing formula description convention, and in that sense is independent even of the general architecture of the machine being studied.

Writing an interpretive trace program is basically a straightforward exercise, but there are two classes of problems. The first are a consequence of the hardware architecture, and may require some awkward but tractable solutions. The requirement for having a base register for the trace program, for example, is often made difficult by instructions which can potentially modify all registers, such as Load Multiple. The second and more serious class of problems are a consequence of the software architecture.

Figure 1: Measurement System

The manufacturer's hardware manual is a complete and accurate description of all instructions except one: Super-The operating system makes SVC a visor Call (SVC). difficult and unpredictable instruction to trace, primarily because of the variety of cases in which control is not transferred to the instruction following the SVC. half of the trace interpreter is devoted to problem SVC's, such as LINK (dynamic transfer to a relocatable program file), SPIE (create a program-interrupt environment), EOV (test for unusual file conditions), and many others. would be to the great benefit of many computer users if the designers of software were required to be as accurate and complete in the description of their systems as the designers of hardware.

#### 3.2 VERIFICATION

This section explains the procedure for verifying cache miss and SVC times, describes the benchmark jobs used, and shows the computation of predicted times and comparison with benchmark runs.

# 3.2.1 Cache Miss Penalty

Although cache miss penalty information is available from the manufacturers, it was difficult to interpret precisely what the effect on instruction time is. Since measurements are not difficult and the correction could be

significant, the values were verified experimentally. To determine the cost of a cache miss, a test program simply fills the cache with known data. A second loop is then timed, in which either the same data is reloaded, or new data displaces the old. The difference in time between the two versions of the second loop, divided by the number of cache misses caused by the loop which displaces the data, provides the cache miss time. The value found for IBM is 480 nsec, which is not inconsistent with the (rather confusing) information from the hardware manuals. For Amdahl, cache misses are found to cost 650 nsec, which also agrees with information from the designers.

Once the cache miss penalty is established, the effect of a supervisor request on the user data in the cache can be measured easily. In a similar fashion the cache is filled with known data, the SVC is issued, and the cache is refilled with the same data. The second loop is timed, and compared to the identical loop when the SVC is not present. The time difference divided by the cache miss penalty gives the number of cache lines that were displaced by the SVC. Note that the second loop must fill the cache in the opposite order from the first loop, otherwise the LRU replacement algorithm would cause the original data to be removed instead of the data added by the SVC. Table 1 shows the fraction of cache displacement for some of the more common supervisor requests.

Table 1.

SVC Times and Cache Requests

(Averaged for all programs)

|          |          | IBM       | Amdahl   |           |  |

|----------|----------|-----------|----------|-----------|--|

| Name     | CPU time | % cache   | CPU time | %cache    |  |

|          | usec.    | displaced | usec.    | displaced |  |

| OPEN     | 26658    | 100%      | 17605    | 100%      |  |

| CLOSE    | 16929    | 100%      | 13488    | 100%      |  |

| EXCP I/O | 107      | 58%       | 101      | 24%       |  |

| WAIT     | 234      | 16%       | 139      | 7%        |  |

| REGMAIN  | 394      | 30%       | 219      | 17%       |  |

| LINK     | 3629     | 100%      | 1613     | 41%       |  |

| OVERLAY  | 5214     | 100%      | N/A      | N/A       |  |

One of the interesting differences of implementation between the two machines is the effect of data stores on the cache. The IBM approach is to always store data directly into main memory, and to update the cache only if the line already exists. The Amdahl machine updates the cache line if the data is present without storing into main memory. If the data is not in the cache, the line will be read from memory. If the replacement algorithm must remove a line which was modified in the cache, the memory is updated at the time the line is replaced. The IBM method, called "store-through", has often been criticized because requires a main memory access for all stores [KAP]. Although the store can proceed in parallel with subsequent instructions, any subsequent main memory accesses must be suspended until the memory becomes available. Since the timing formulas do not explicitly account for this effect, it is important to determine its magnitude.

There are three factors which combine to minimize the possible deliterious effects of the store-through policy used by IBM. The first is that the memory is organized with four-way interleaving of adjacent doublewords, so that consecutive stores may well reference separate memory banks. The second is simply that based on the opcode pair distribution we have accumulated, consecutive instructions which store data into memory are relatively infrequent. The third is that even for pairs of such instructions, there is a level of buffering for data that is to be written to main memory, at least for the case when that data is also in the cache. A penalty appears only for the third consecutive store, and then is 360 nsec. The full write cycle time penalty of 640 nsec occurs only for the fourth and subsequent store. These factors are sufficient to justify not including a correction for store-through writes.

#### 3.2.2 SVC Times

As previously discussed, the CPU time charged for SVCs was measured in order to be able to correct the time given by the operating system. The time charged for each SVC is often large and varies from program to program even for the same SVC type. To account for these variations the time charged to the user for each SVC was measured as the benchmark programs were being traced. The SVC correction computed by summing the measured SVC times is therefore

quite accurate for the 168 because it was the machine used for the tracings. For the 470, the timing program LTIMER was used to give estimates of the average SVC costs. This latter method does not take into account the variation from program to program and the SVC corrections are much less accurate than for the 168. Table 1 shows the time charged for some important SVCs averaged over all programs.

It is interesting that the time charged for supervisor services is often comparable to what would be required if there were no operating system. For I/O operations, previous measurements have shown that the hardware I/O instructions (SIO, TIO, etc.) are incredibly expensive; 100 usec is not unusual [JAY]. This is to be compared with, for instance, the measured charge of 107 usec for the request to the operating system for an I/O operation. Note that both of these are more than two orders of magnitude larger than, for example, the 0.61 usec needed for a double precision floating point multiplication. It would seem that improvements in the arithmetic units of computers have not been accompanied by similar improvements in the I/O interface despite the existence of I/O channels.

# 3.2.3 Benchmark Jobs

The results presented here are derived from the complete analysis of seven benchmark jobs written at the Stanford Linear Accelerator Center<sup>2</sup>. Except for one

(LINSY2) they were all production jobs written for purposes other than performance evaluation. To avoid biasing the results with artifacts from specific languages or programs, we purposely chose the three most used language compilers and programs compiled by them.

- FORTC is a compilation by the IBM Fortran-H optimizing compiler.

- 2. FORTGO is the execution of the FORTRAN program compiled by FORTC. It is a numerical analysis program which solves partial differential equations.

- 3. PLIC is a compilation by the IBM PL/I-F compiler.

- 4. PLIGO is the execution of a PL/I program which accumulates and prints accounting summaries from computer use information.

- 5. COBOLC is a compilation by the IBM ANSI Standard COBOL compiler.

- 6. COBOLGO is the execution of a COBOL program which reformats and prints computer use accounting information.

<sup>&</sup>lt;sup>2</sup>Dozens of other jobs were traced to provide other data presented elsewhere, but only these seven were fully analyzed and run in carefully controlled benchmark conditions on both machines. Several hundred million instructions were traced and analyzed in the course of this study.

7. LINSY2 is the execution of a FORTRAN subroutine which solves large-order simultaneous equations.

No I/O is done.

Table 2 summarizes some characteristics of the benchmark jobs.

Table 2.

Program Characteristics

| Program | # Instr.   | Data<br>reads | Data<br>writes | Inst/Cache Miss |        |

|---------|------------|---------------|----------------|-----------------|--------|

| Program | # Instr.   | per inst      |                | IBM             | Amdahl |

| COBOLC  | 6,048,476  | 0.431         | Ø <b>.</b> 13Ø | 82.57           | 36.95  |

| FORTGO  | 23,865,168 | Ø.352         | 0.204          | 104.06          | 28.07  |

| PL1G0   | 23,863,497 | 0.473         | Ø.261          | 73.28           | 61.16  |

| LINSY2  | 11,719,853 | Ø.195         | 0.067          | 20597           | 19598  |

| COBOLGO | 3,559,533  | Ø.738         | Ø.453          | 13.42           | 30.93  |

| FORTC   | 17,132,697 | Ø.433         | Ø.146          | 39.86           | 24.47  |

| PL1C    | 24,338,101 | Ø.379         | 0.137          | 145.33          | 63.48  |

## 3.2.4 <u>Validation</u>

Verification basically consists of comparing the time predicted by our model for each benchmark job with the corrected real execution time. The time predicted for each benchmark, Tpred, consists of the following terms:

Tins, the total time predicted from the timing formulas, which does not include the cache miss penalty.

M \* Tmiss, where M is the number of cache misses as reported by the cache simulator, and Tmiss is the cache miss penalty. The number of cache misses includes the effect of SVC execution on the cache contents.

Tcross, the time penalty, for Amdahl only, paid when references to the cache cross a line boundary. The penalty is two cycles (.065 usec) for reads and three cycles (.0975 usec) for writes, and is computed using numbers provided by the cache simulator. Virtually all the penalty arises from instruction fetch, since none of the programs access unaligned data. There is no equivalent penalty for IBM because its larger instruction buffer prefetches enough so that two successive doublewords can be accessed without introducing an additional delay.

The corrected time for the actual execution, Trun, consists of the following terms:

Tacc, the time as given by the standard IBM accounting routines.

<u>-Tsvc</u>, the time attributed to the user for the execution of all the supervisor calls, which must be subtracted from Tacc. Table 3 provides the values for each of these times for each of the benchmarks. For Tpred and Trun, the relative percentage of each of their components is given. The absolute error, Trun-Tpred, and the percent error, (Trun-Tpred)/Trun, appears on the last lines. The verification process points to large discrepancies between the basic execution time of instructions (Tins) and the speed as perceived by the user (Tacc).

There are a variety of methodological problems involved in accurate benchmarking. Because these were real programs doing I/O to real devices and interacting in complex ways with the operating system, it was very difficult to get accurate and repeatable measurements. In order to achieve accuracy to within about 1%, it was necessary to carefully control running conditions: using otherwise idle time at night (the computers are normally multiprogrammed), removing operating system variations by specific device allocations, memory control to isolate paging variations, etc. program was run many times, and the resulting averages were used only if the deviation with particular set of conditions was small; these same conditions were then used during the tracing phase. The goal of repeatable measurements was achieved, but the difficulty of doing so was rather more than expected.

Table 3.

Predicted and Benchmark Times

COBOLC

---- IBM ---- Amdahl --- RATIO

| CODOLC                             | Time %                                   | Time                   | 8                                          | IBM/Amd       |

|------------------------------------|------------------------------------------|------------------------|--------------------------------------------|---------------|

| Tins<br>M*Tmiss<br>Tcross<br>Tpred | 2.213 98.4<br>035 1.5<br>2.248 100.6     | .106<br>.048           | 3.60                                       | .330          |

| Tacc -Tsvc Trun                    | 2.57 100.0<br>.348 13.5<br>2.222 86.4    | .320                   |                                            | 1.088         |

| Trun-Tpred % error                 | 026<br>-1.170                            | 057<br>-4.101          | nen ten enn eint eint mit eint eint eint e |               |

| FORTGO                             | IBM<br>Time %                            | Time                   |                                            | IBM/Amd       |

| Tins<br>M*Tmiss<br>Tcross<br>Tpred | 6.176 98.29<br>.110 1.79<br>6.286 100.00 | 3.286<br>5.553<br>.082 | 83.81<br>14.10<br>2.09                     | 1.879<br>.199 |

| Tacc<br>-Tsvc<br>Trun              | 6.42 100.00<br>.082 1.23<br>6.338 98.73  | <u> </u>               |                                            |               |

| Trun-Tpred                         | .052<br>0.82                             |                        |                                            |               |

| PL1GO                              | IBM<br>Time %                            | Time                   |                                            | IBM/Amd       |