# DYNAMIC CONTROL STRUCTURES AND THEIR USE IN EMULATION\*

# VICTOR R. LESSER STANFORD LINEAR ACCELERATOR CENTER STANFORD UNIVERSITY Stanford, California 94305

PREPARED FOR THE U. S. ATOMIC ENERGY

COMMISSION UNDER CONTRACT NOS.

AT(04-3)-515 and AT(04-3)-326, P.A. No. 23

#### October 1972

Printed in the United States of America. Available from National Technical Information Service, U. S. Department of Commerce, 5285 Port Royal Road, Springfield, Virginia 22151.

Price: Printed Copy \$3.00; Microfiche \$0.95.

<sup>\*</sup>Ph.D. Dissertation.

DEDICATED TO THE MEMORY OF MY FATHER

REUBEN DAVID LESSER

WHOSE INSPIRATION HAS FINALLY BLOSSOMED

#### ABSTRACT

This thesis describes an architecture for a parallel microcomputer system that permits a systematic and flexible approach to the emulation of a wide variety of complex sequential and parallel intermediate machine languages in a dynamically varying Processor-Memory-Switch (PMS) environment. This architecture is based on the view that complex emulators can be best structured in terms of a set of microprocessors that interact in a highly structure manner. These highly structured interaction patterns are defined through the concept of a virtual PMS environment. This concept embodies the capability for reconfiguring both the internal and the external environment of a microcomputer system: the number of internal working registers of each microprocessor; the structure of memory, e.g., its size and word length; and the number of microprocessors and functional units, and their interconnection and interaction patterns. The virtual PMS is implemented in the microcomputer architecture by adding a new global level of hardware control. A particular virtual PMS is dynamically defined by modifying the syntax (i.e., the number of data elements and their relationship) of the data structure for control used by this global hardware control level.

The representational capabilities of this architecture have been examined through the microprogramming of an emulator for a sophisticated parallel machine language, Adams' Graph Machine Language. The emulator of this machine language has demonstrated the versatility and usefulness of the concept of a virtual PMS by requiring less than 600 64-bit microinstructions to be programmed, while at the same time being able to exploit fully the implicit parallelism of a graph machine program. In addition, the dynamic execution characteristics of this architecture have been studied through the use of a detailed simulator of a hardware organization for this microcomputer architecture. The simulator has been used to verify quantitatively that this organization permits parallel activity on the virtual PMS to be mapped without significant overhead onto the physical PMS. In particular, the simulation results indicate that where sufficient parallel activity exists, the addition of microprocessors to the PMS configuration will reduce in a linear way the time it takes to execute the computation. The simulation results have also indicated that the logical hardware design, with the appropriate PMS configuration, can efficiently handle sustained parallel activity, involving highly structured interaction patterns, of greater than sixteen microprocessors.

#### Acknowledgements

I wish to express my sincere thanks to Professor William F. Miller who has shepherded me through this long arduous thesis. I would also like to acknowledge the advice, support and friendship given to me by the other members of my reading committee — Professors Edward Davidson, Harry Saal and Forest Baskett — without which I would never have finished. Over the years there have been many people whose encouragement of my research efforts and fruitful discussions have been very important to my work. Special thanks to Professors William McKeeman, Robert Fabry and Alan Kay, and to my fellow graduate students and friends Lee Erman, Bill Riddle and John Levy. I would also like to thank Edward Nelson for the considerable effort he devoted on my behalf so that I could use his graph program simulator.

There have been many other people who have been very helpful in preparing this manuscript — Harriet Canfield for her numerous retypings, Joe Wells for his help in using WYLBUR, and finally to Guynn Perry and Hugo Smith for their help in the final moments.

Finally, I would like to acknowledge the deep debt of gratitude I owe to my Uncle Harold Freed, whose friendship, support, advice and even criticism I will always cherish.

# TABLE OF CONTENTS

|     |     |       |                                                                       |       |      |   | Page |

|-----|-----|-------|-----------------------------------------------------------------------|-------|------|---|------|

| I.  | Int | roduc | tion                                                                  | •     | •    | • | 1    |

|     | 1.  | Unif  | ication of Three Trends in Computer Architecture                      | •     | •    | • | 1    |

|     | 2.  | Appr  | oach to the Design of a New                                           | •     | •    | ٠ | 6    |

|     |     | 2.1   | Traditional Microcomputer Architecture                                | •     | •    | • | 6    |

|     |     | 2.2   | Basis for a New Microcomputer Architecture                            | •     | •    | • | 11   |

|     |     | 2.3   | A New Microcomputer Architecture · · ·                                | •     | •    | • | 19   |

|     | 3.  | An O  | utline of the Justification for this New • Microcomputer Architecture | •     | •    | • | 27   |

| II. | Str | uctur | e Building Language and Data Structure • • for Control                | •     | •    | • | 30   |

|     | 1.  | Moti  | vation and Important Design · · · · · · · Considerations              | •     | •    | • | 30   |

|     | 2.  | Data  | Structure for Control · · · · · ·                                     | •     | •    | • | 32   |

|     |     | 2.1   | External Control Environment · · · · ·                                | •     | •    | • | 36   |

|     |     | 2.2   | External Data Environment                                             | •     | •    | • | 40   |

|     |     | 2.3   | Internal Control Environment                                          | •     | •    | ٠ | 40   |

|     |     | 2.4   | Internal Data Environment                                             | ٠     | •    | • | 42   |

|     | 3.  | Stru  | cture Building Language                                               |       | •    | • | 43   |

|     |     | 3.1   | Single Microprocess Interaction Patterns .                            |       | •    | • | 55   |

|     |     | 3.2   | Multiple Microprocess Interaction Patterns                            |       |      |   | 59   |

|     |     | 3.3   | Microprocess/Functional-Unit Interaction Pa                           | atte  | rns  |   | 62   |

|     |     | 3.4   | Microprocess/Memory-Subsystem Interaction 1                           | Patte | erns |   | 71   |

|     |     | 3.5   | Microprogram Invocation · · · · · ·                                   | •     | •    |   | 73   |

|     | 4.  | Gene  | ration of Data Structure for Control · · ·                            |       |      |   | 74   |

|      |      |                                                                                              | Page |

|------|------|----------------------------------------------------------------------------------------------|------|

| III. | A Co | omprehensive Test Case                                                                       | 84   |

|      | 1.   | Discussion of Adams' Graph Machine Language · · · ·                                          | 85   |

|      | 2.   | The Design of An Emulator for the Adams'                                                     | 90   |

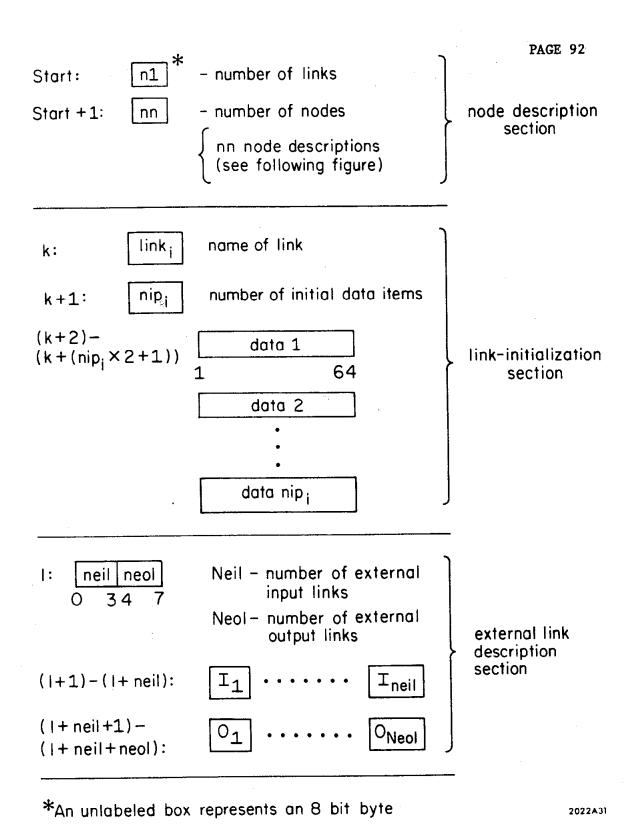

|      |      | 2.1 Machine Language Format and Memory Layout                                                | 91   |

|      |      | 2.2 The CDS for AGML Emulator · · · · · · ·                                                  | 95   |

|      |      | 2.2.1 The CDS for Resource · · · · · · · · · · · · · · · · · · ·                             | 95   |

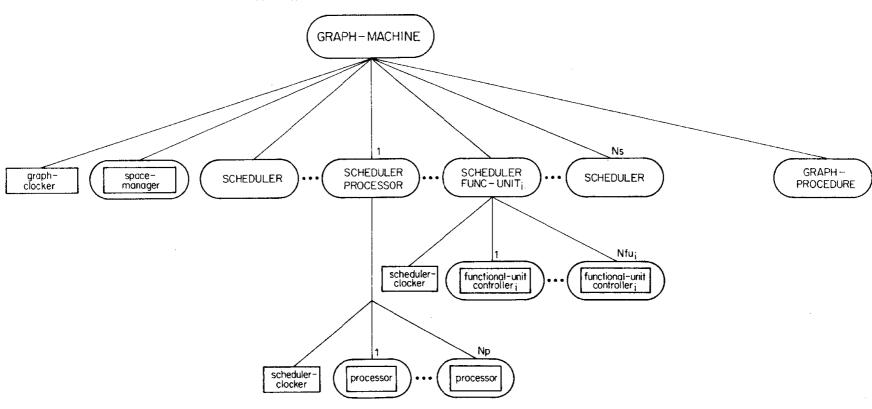

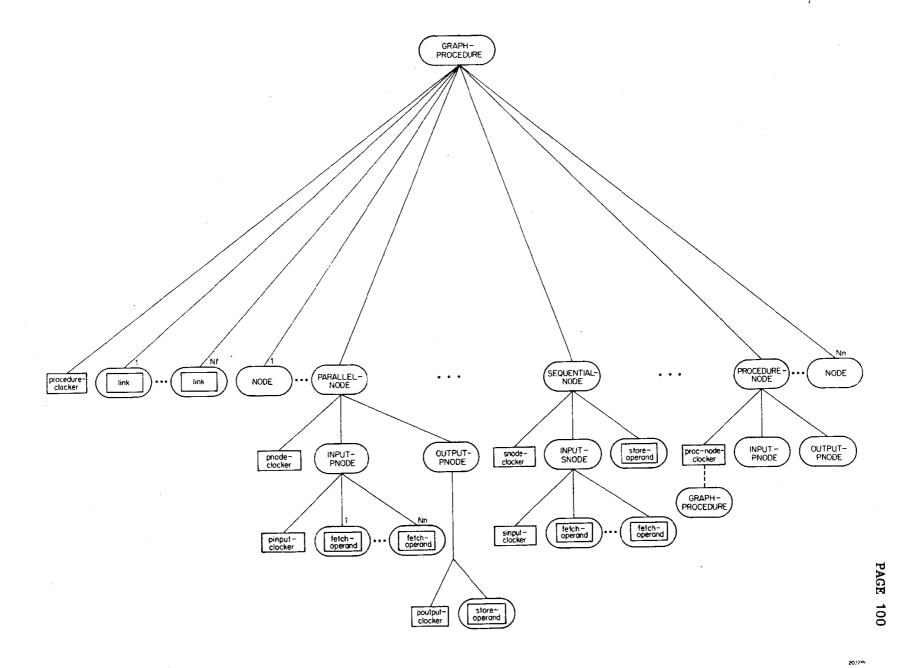

|      |      | 2.2.2 The CDS for Sequencing - · · · · · · · of a Graph Procedure                            | 99   |

|      |      | 2.3 The Microcoding of the Parallel Node · · · ·                                             | 102  |

|      | 3.   | An Evaluation of the Suitability of the SBL for the • • Coding of the Graph Machine Emulator | 112  |

| IV.  |      | ardware Implementation of the Microcomputer · · · · · · · · · · · · · · · · · · ·            | 114  |

|      | 1.   | A PMS for the Microcomputer Architecture · · · ·                                             | 117  |

|      | 2.   | The Interprocessor Communications Structure· · · · and the Virtual Interaction Controller    | 120  |

|      |      | 2.1 Microprocessor Scheduling Strategy · · · · ·                                             | 126  |

|      | 3.   | The Microprocessor Organization · · · · · · · ·                                              | 130  |

| v.   | Sim  | ulation Results • • • • • • • • • • • • • • • • • • •                                        | 137  |

|      | 1.   | Simulator · · · · · · · · · · · · · · · · · · ·                                              | 138  |

|      |      | 1.1 Configuring the Simulator · · · · · · ·                                                  | 138  |

|      |      | 1.2 Summary Statistics of the Simulator · · · ·                                              | 141  |

|      | 2.   | Dynamic Performance characteristics of the AGML · · · Emulator and the Hardware Organization | 147  |

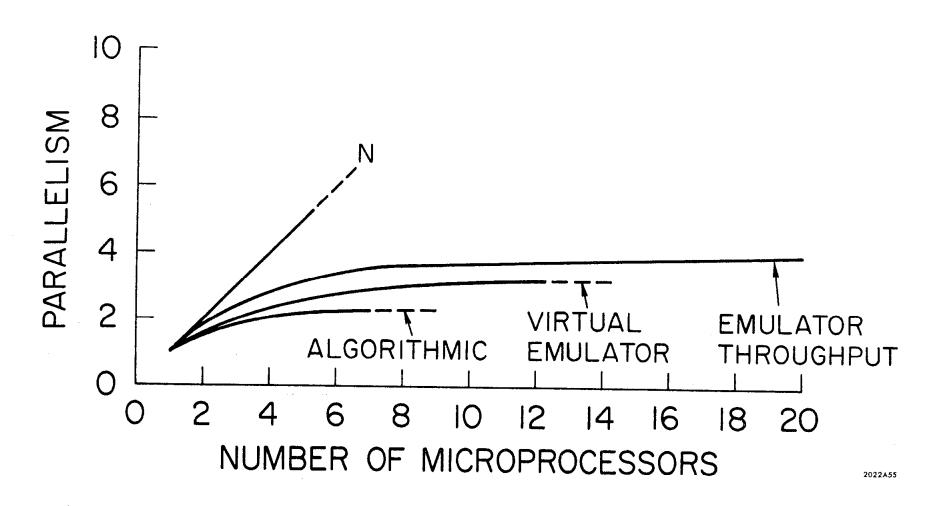

|      |      | 2.1 Measuring Parallel Activity · · · · · ·                                                  | 150  |

|      |      | 2.2 Dynamic Performance Characteristics of the · · · AGML Emulator                           | 155  |

|                                                                            |     | Page |

|----------------------------------------------------------------------------|-----|------|

| 2.3 Dynamic Performance Characteristics of the · · · Hardware Organization | . • | 160  |

| 2.4 Future Research - Choosing a PMS Configuration                         |     | 170  |

| VI. Summary Comment and Conclusions · · · · · · · ·                        | • • | 176  |

| References: · · · · · · · · · · · · · · · · · · ·                          | • • | 185  |

| Appendices:                                                                |     |      |

| A. Integer Function Language                                               | • • | 190  |

| B. MicroAssembler Syntax                                                   |     | 197  |

| C. Listings of Graph Machine Emulator                                      |     | 204  |

| D. The Internal Format of Sum-Squared Graph Program(5)                     |     | 239  |

# LIST OF FIGURES

|      |                                                                                                |   |   | Page |

|------|------------------------------------------------------------------------------------------------|---|---|------|

| 1.   | Mapping of a Higher Level Language to a Machine Language                                       | • | • | 3    |

| 2.   | The Relationship between the Emulation Process and . a Conventional Microcomputer Architecture | • | • | 8    |

| 3.   | Horizontal (minimal encoded) Microcode Format of . IBM 360/50                                  | • | • | 9    |

| 4.   | Vertical (highly encoded) Microcode Format of MLP-900                                          |   | • | 10   |

| 5.   | Conceptual Program Structure of an Emulator · · ·                                              | • | • | 12   |

| 6.   | Commutative State Diagram of Conventional Emulation Process                                    | ٠ | • | 13   |

| 7a.  | A New View of Emulation Process · · · · · ·                                                    | • | • | 21   |

| 7b.  | A New View of Commutative State Diagram of Emulation Process                                   | • | • | 22   |

| 8.   | A New View of Relationship between Emulation Process and Microcomputer Architecture            | • | • | 24   |

| 9a.  | Structure of Microprocess State Vector · · · ·                                                 | • | • | 33   |

| 9Ъ.  | Functional Classification of Microprocess State · · Vector Components                          | • | ٠ | 35   |

| 10.  | Control Data Structure for a Pipelined Emulator of a<br>Conventional Computer                  | • | ٠ | 37   |

| 11.  | Microprogram Memory Format                                                                     | • | • | 47   |

| 12.  | Substructure of Process State                                                                  | • |   | 56   |

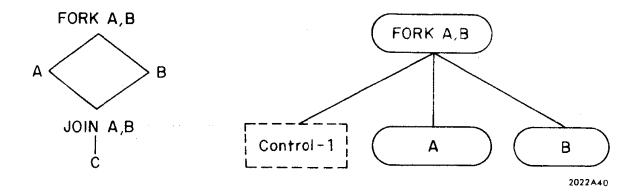

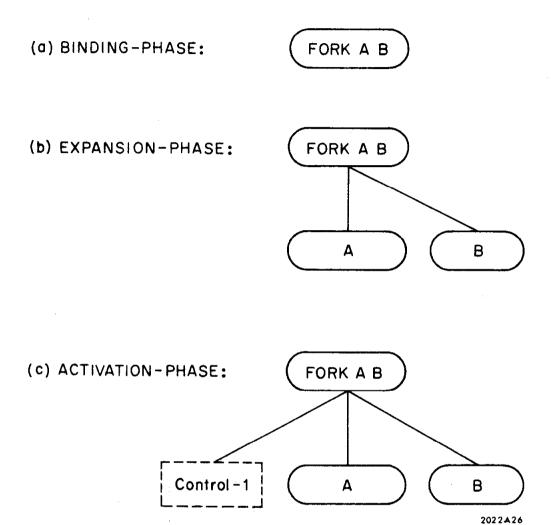

| 13.  | Control Data Structure for a FORK Control Structure                                            |   | • | 61   |

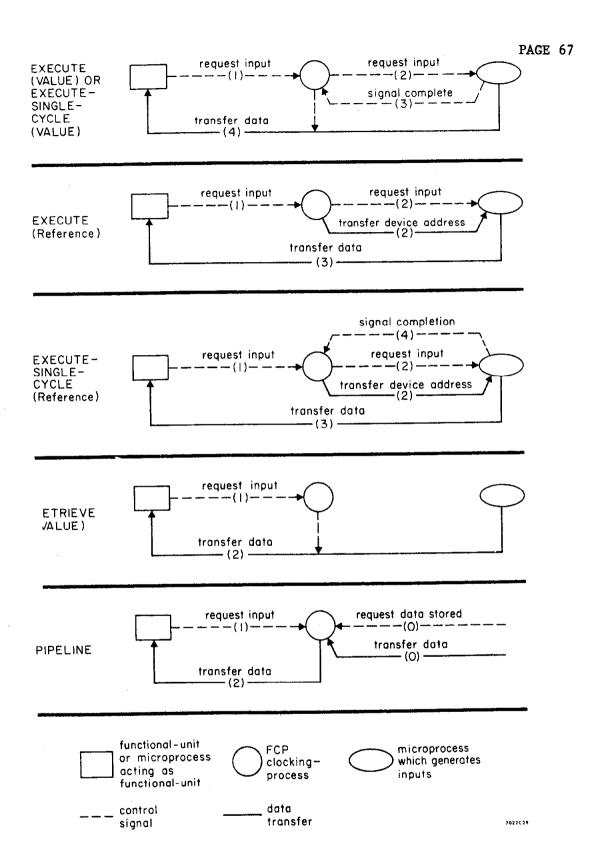

| 14.  | Schematic of Input Request Protocol · · · · ·                                                  |   | • | 67   |

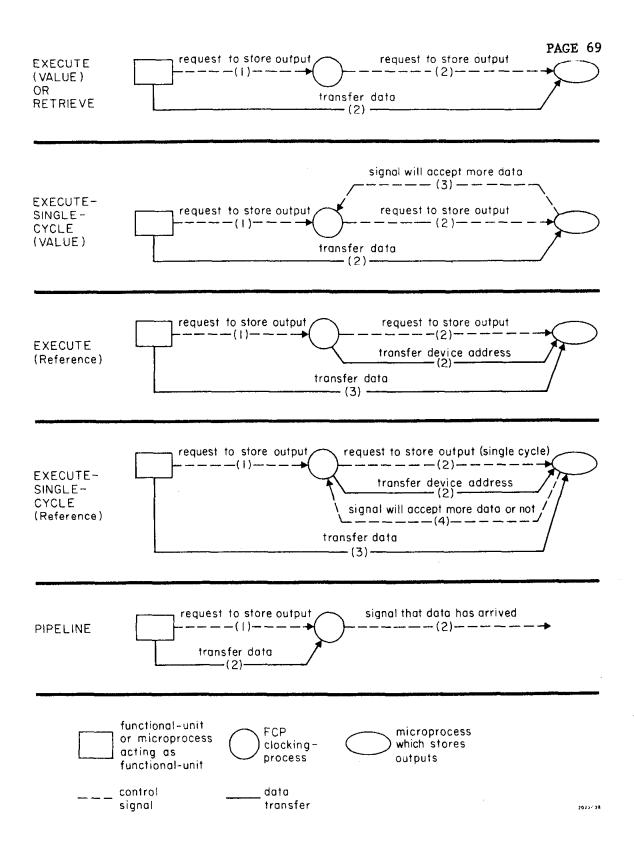

| 15.  | Schematic of Output Request Protocol · · · ·                                                   | • | • | 69   |

| 16.  | Three Phases of Microprocess Execution · · · ·                                                 |   | • | 77   |

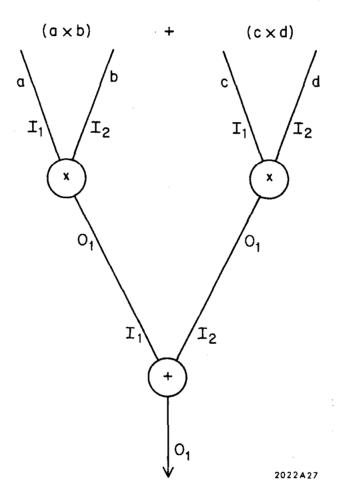

| 17.  | A Simple Graph Program · · · · · · · · · · · · · · · · · · ·                                   | • | • | 86   |

| 18a. | Machine Language Format for a Graph Procedure · ·                                              | • | • | 92   |

| 18Ъ. | Machine Language Format for a Node · · · · ·                                                   |   |   | 94   |

|      |                                                                                         | Page |

|------|-----------------------------------------------------------------------------------------|------|

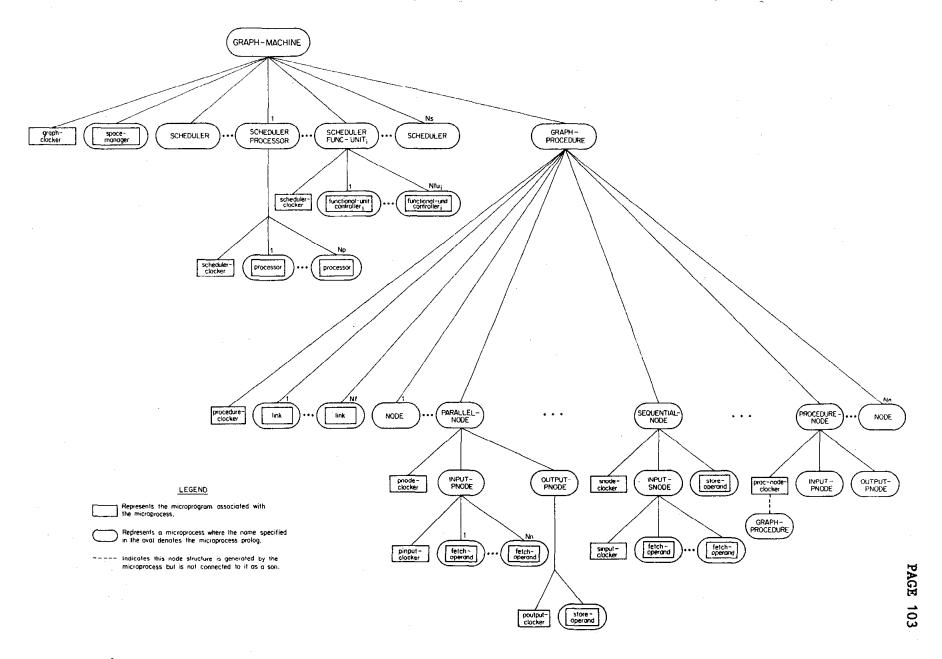

| 19a. | Control Data Structure for Resource Management                                          | 97   |

| 19ъ. | Control Data Structure for GRAPH-PROCEDURE                                              | 100  |

| 19c. | Control Data Structure for AGML                                                         | 103  |

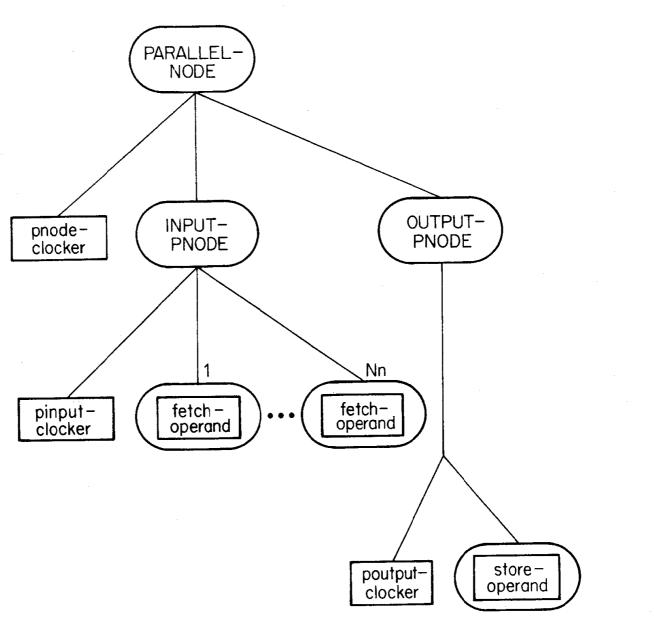

| 20a. | Control Data Structure for PARALLEL-NODE                                                | 104  |

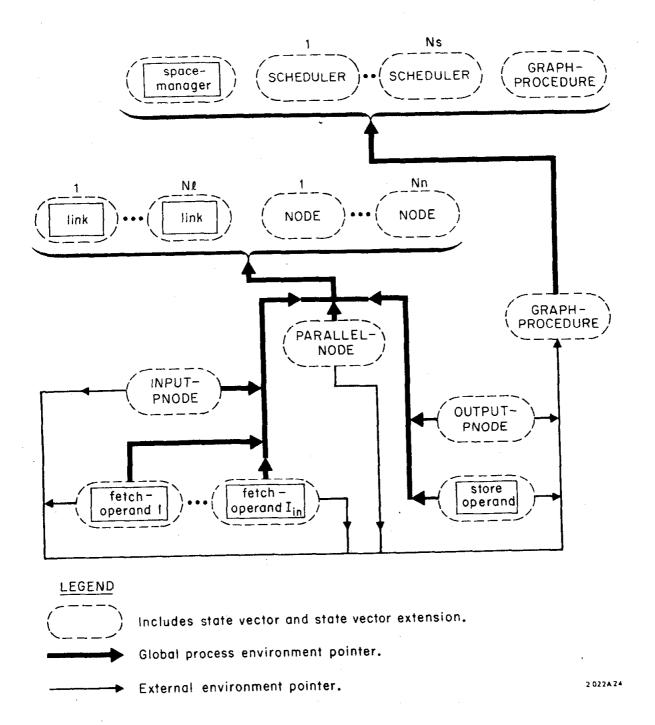

| 20ъ. | Control Environment of PARALLEL-NODE                                                    | 106  |

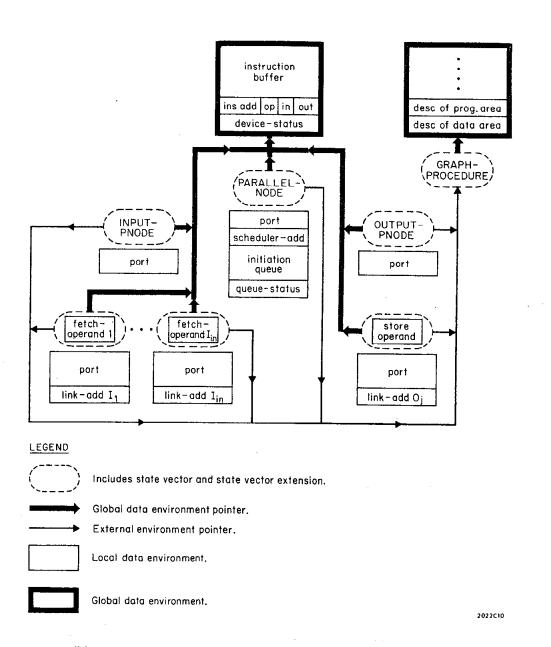

| 20c. | Data Environment of PARALLEL-NODE                                                       | 107  |

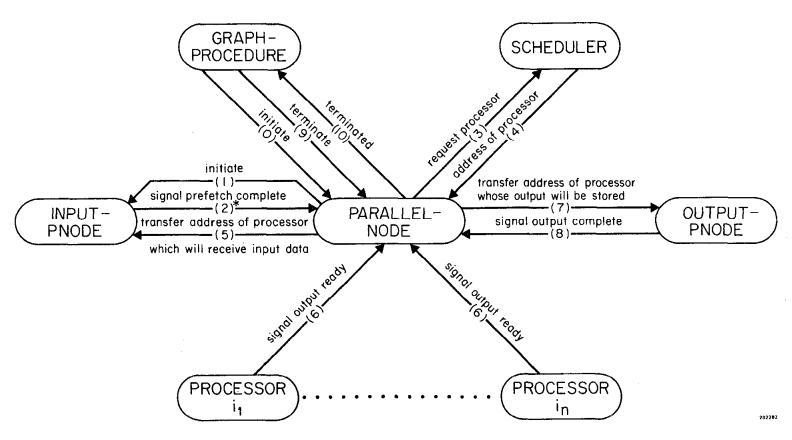

| 21.  | Interaction Patterns of PARALLEL-NODE                                                   | 108  |

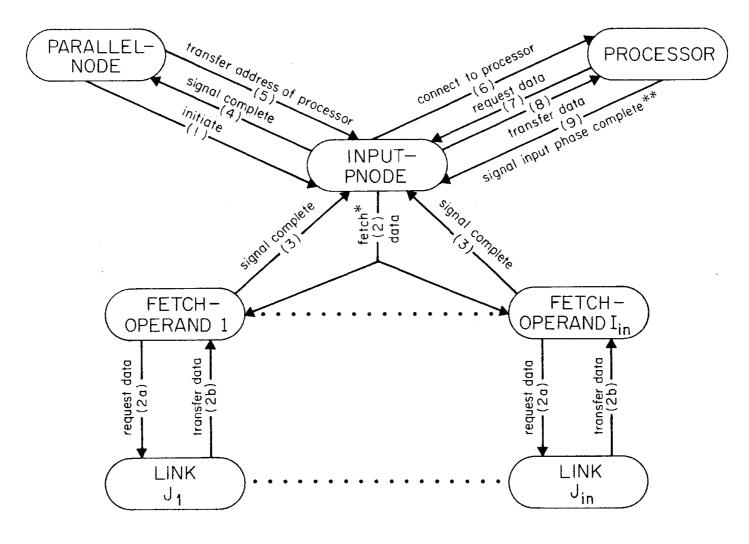

| 22.  | Interaction Patterns of INPUT-PNODE                                                     | 111  |

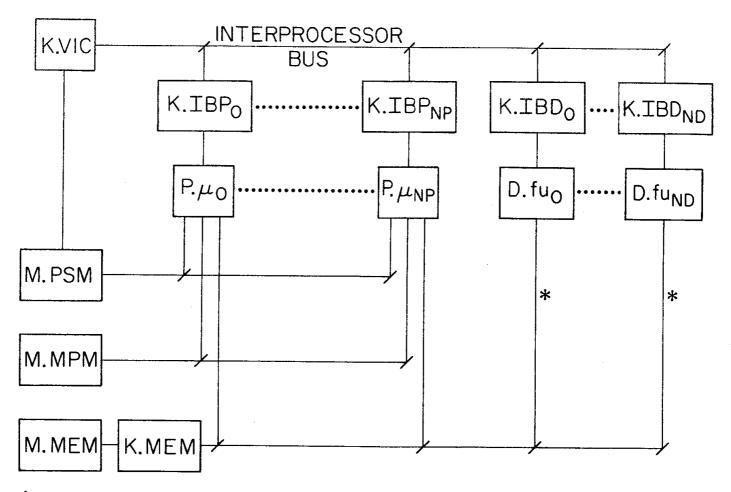

| 23.  | PMS for Microcomputer Architecture · · · · ·                                            | 118  |

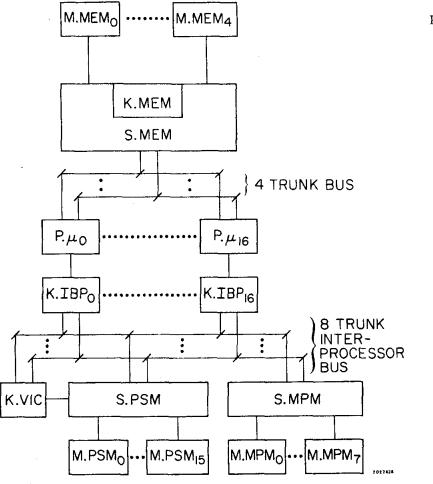

| 24.  | A Detailed PMS for Microcomputer Architecture                                           | 121  |

| 25.  | An Example of a System Configuration for the Simulator .                                | 140  |

| 26a. | An Example of Microprocessor Subsystem Performance · · · Statistics                     | 142  |

| 26Ъ. | An Example of M.PSM and M.MPM Performance Statistics                                    | 143  |

| 26c. | An Example of M.MEM Performance Statistics                                              | 144  |

| 26d. | An Example of Processor Utilization Statistics                                          | 145  |

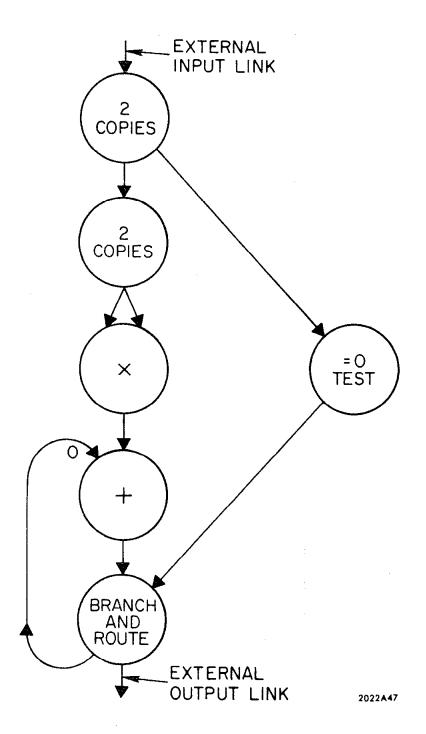

| 27.  | Sum-Squared Graph Program                                                               | 148  |

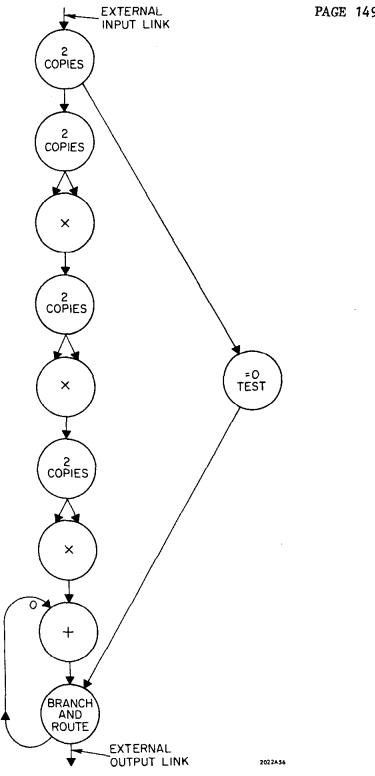

| 28.  | Sum-Eighth-Power Graph Program                                                          | 149  |

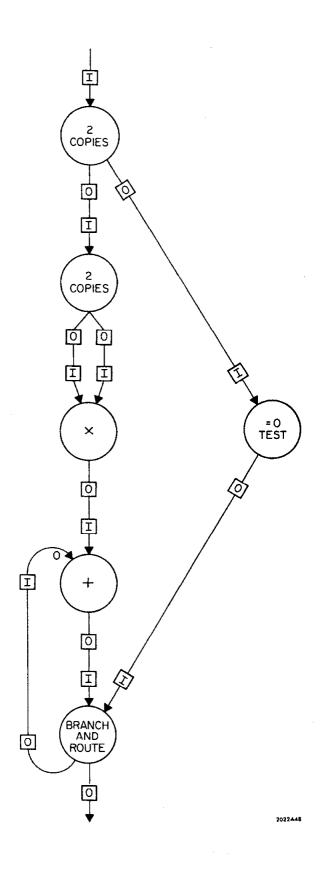

| 29.  | Three Levels of Parallel Activity Measurement                                           | 151  |

| 30.  | Modification to Sum-Squared Graph Program to Measure Program Implementation Parallelism | 154  |

| 31.  | Performance Characteristics of AGML Emulator on Sum-Squared Graph Program(5)            | 156  |

| 32.  | The Effect of Hardware and Program Interference on Sum-Eighth-Power Graph Program(10)   | 158  |

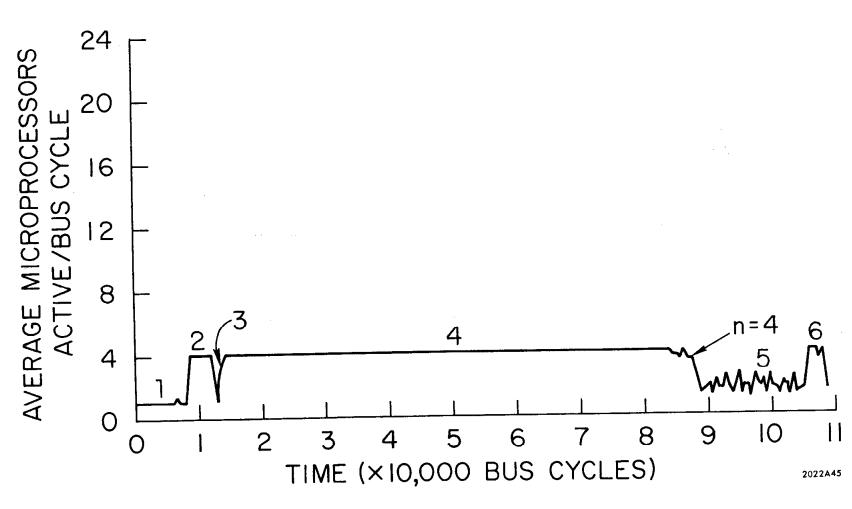

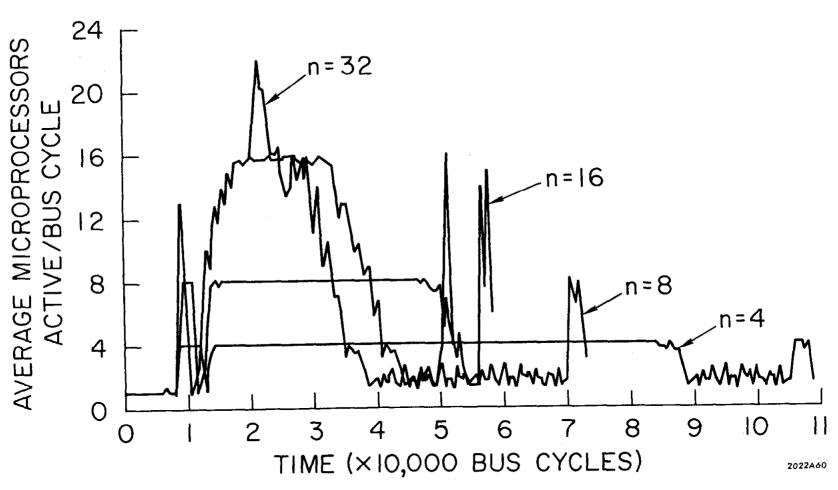

| 33a. | Microprocessor(4) Utilization Curve for Sum-Eighth-Power • Graph Program(10)            | 161  |

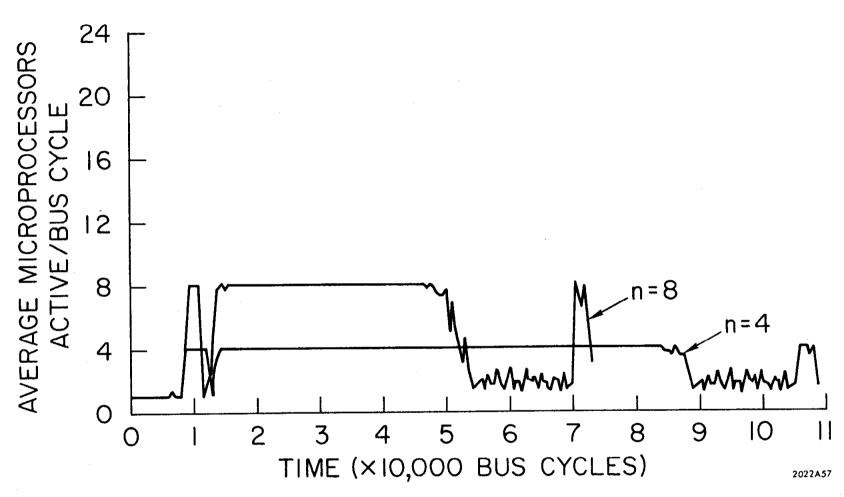

| 33ь. | Microprocessor (4 vs 8) Utilization Curve Sum-Eighth-Power Graph Program(10)            | 162  |

|      |                                                                                                                                                                               | Page     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

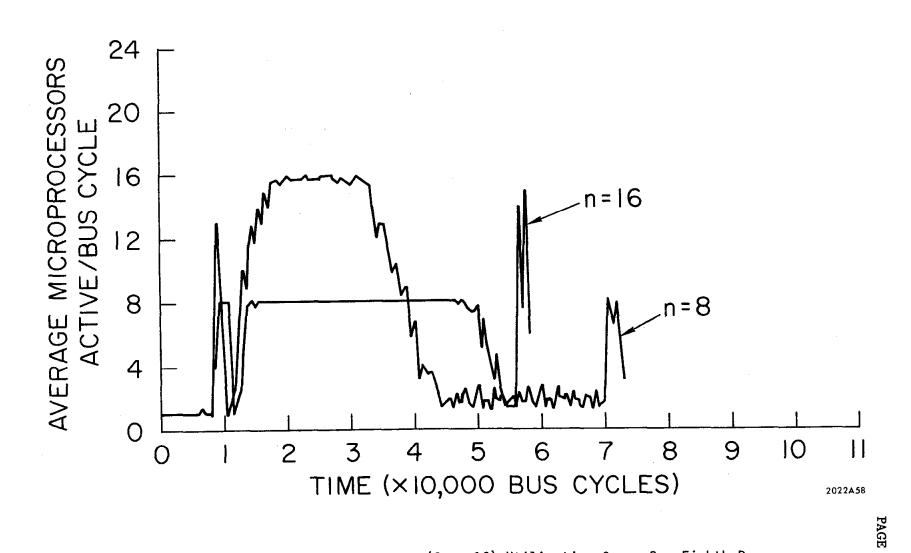

| 33c. | Microprocessor (8 vs 16) Utilization Curve Sum-Eighth-Power Graph Program (10)                                                                                                | 163      |

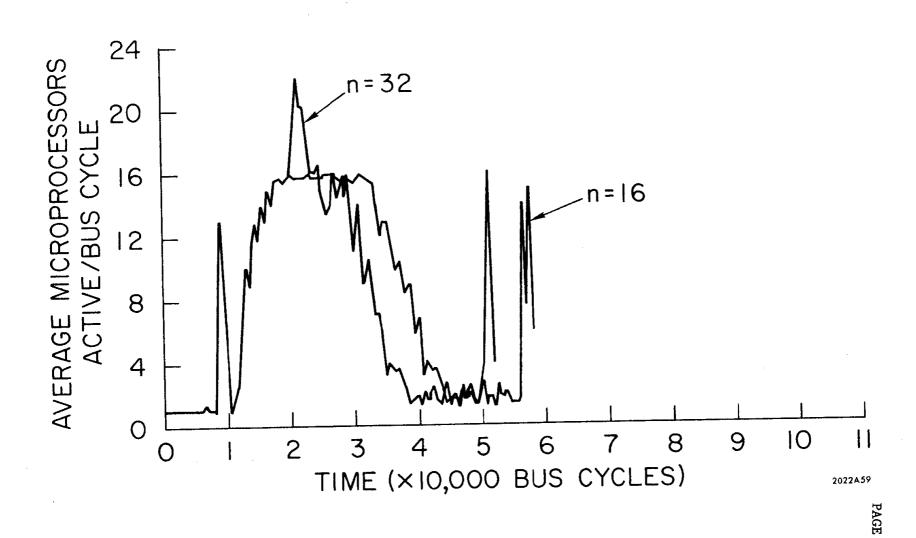

| 33d. | Microprocessor (16 vs 32) Utilization Curve Sum-Eighth-Power Graph Program(10)                                                                                                | 164      |

| 33e. | Microprocessor (4,8,16,32) Utilization Curve Sum-Eighth-Power Graph Program(10)                                                                                               | 165      |

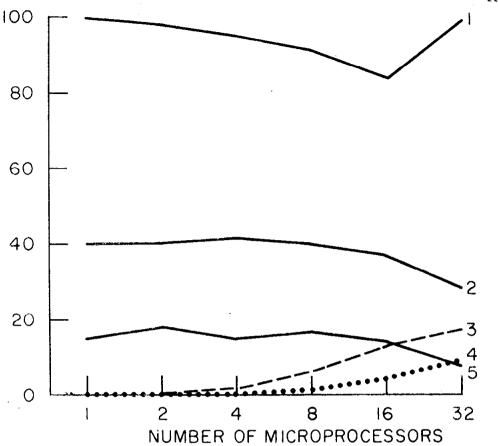

| 34.  | Distribution of Hardware Interference for Sum-Eighth-Power Graph Program(10)                                                                                                  | 168      |

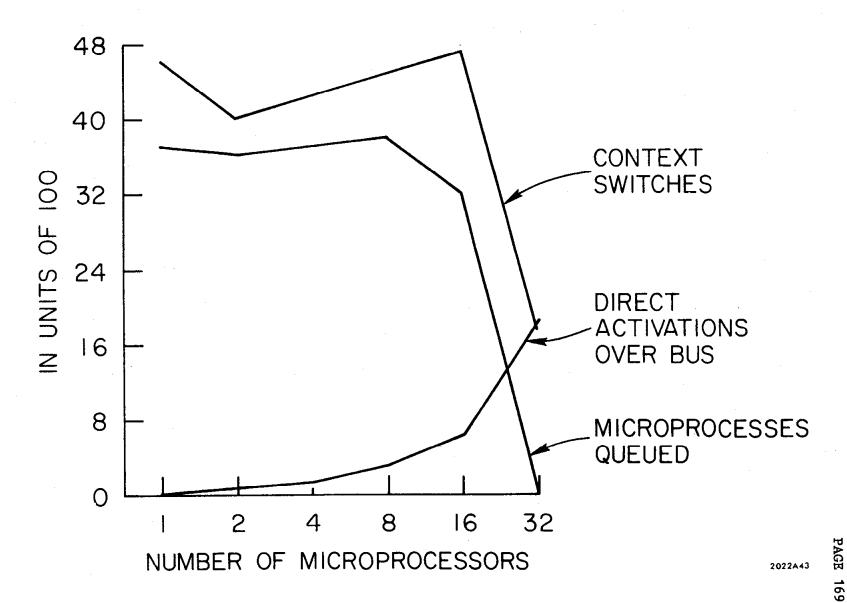

| 35.  | Effect of Varying the Number of Microprocessors on Number of Context Switches, Interprocessor Communications, and Microprocesses Queued for Sum-Eighth-Power Graph Program(10 | 169<br>) |

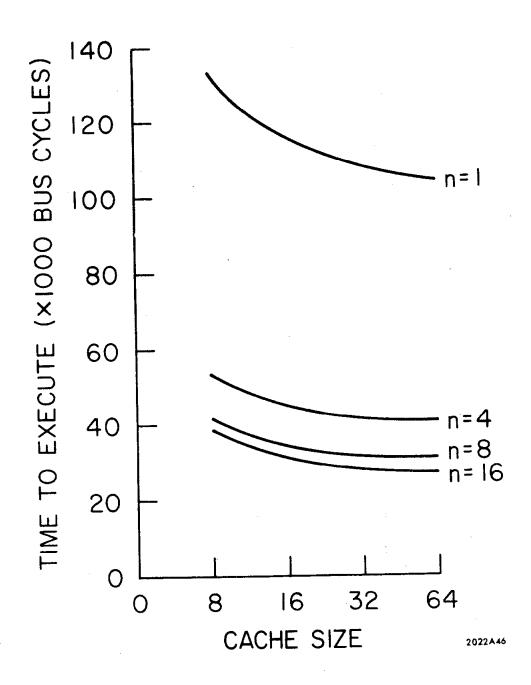

| 36a. | Effect of Cache Size on Throughput of Sum-Squared Graph Program(5)                                                                                                            | 171      |

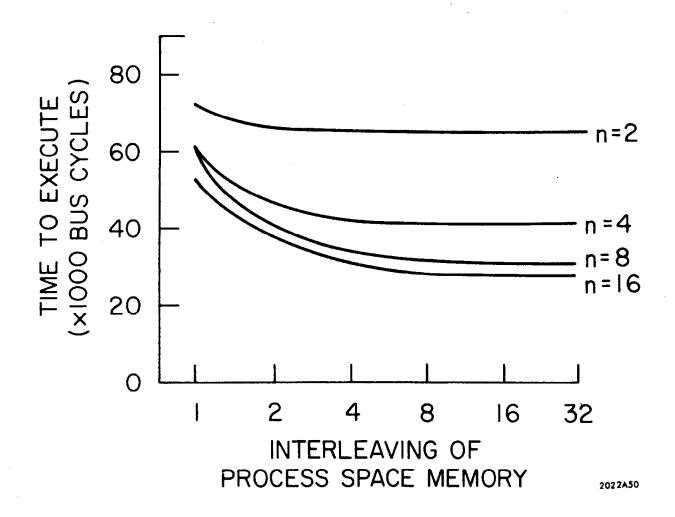

| 36ъ. | Effect of Process Space Memory Interleaving on Throughput of Sum-Squared Graph Program(5)                                                                                     | 172      |

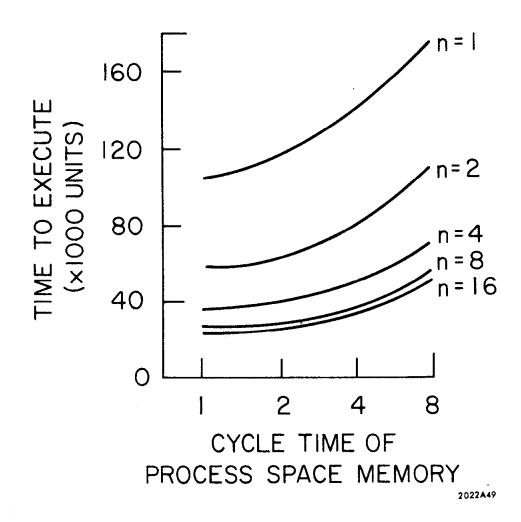

| 36c. | Effect of Process Space Memory Cycle Time on Throughput . of Sum-Squared Graph Program(5)                                                                                     | 173      |

| 37.  | Format of IFL Microinstruction Word                                                                                                                                           | 192      |

|    | LIST OF TABLES                                            | Page |

|----|-----------------------------------------------------------|------|

| 1. | SBL (Structure Building Language) Instructions            | 45   |

| 2. | Agreeable Communication States                            | 51   |

| 3. | Input Request Protocol for Control of Functional Units    | 66   |

| 4. | Output Request Protocol for Control of Functional Units . | 68   |

| 5. | PMS Configuration Used for Simulation Results             | 175  |

| 6. | IFL Operation Codes                                       | 196  |

#### I. INTRODUCTION

"Pragmatically important problems such as the design of programming languages appropriate for given problem areas, design of computer systems well matched to given programming languages, and defining efficient structures for translators are capable of being adequately handled only within a model that assigns similar structures to programming languages and computer languages both globally and locally". (Nar67)

## I.1 Unification of Three Trends in Computer Architecture

Over the past few years, there has been a growing trend toward the design of computers whose architecture differs considerably from that of the classic von Neumann type computer\*. This departure from the von Neumann type computer architecture has occurred on three levels: 1) the Instruction-Set-Processor (ISP) level of which the Burroughs B5500 is an example, 2) the PMS Processor-Memory-Switch (PMS) level of which the ILLIAC-IV is an example, and 3) the Processor Implementation Technique (PIT) level of computer design of which the IBM 360/40 is an example (terminology from BEL70).

The first trend, that is on the Instruction-Set-Processor level, has led to the development of computers whose machine languages

<sup>\*</sup>A von Neumann type computer is considered to have a sequential control structure, and instructions which operate on single units of data accessed from a linear address space.

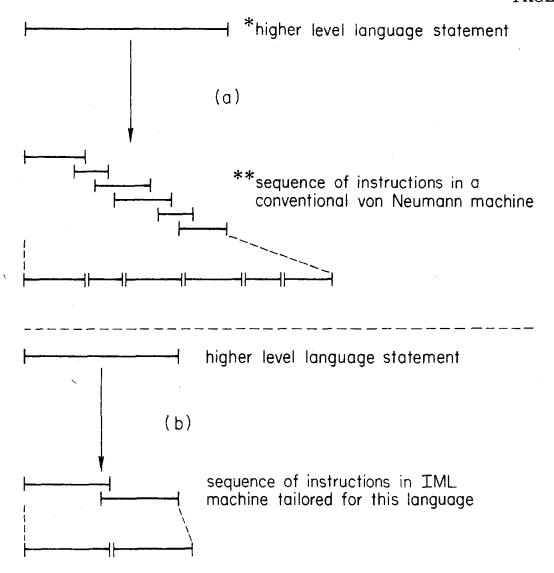

are optimized for a particular higher level language or operating system environment. This trend is exemplified in the languages of machines such as the Burroughs B6500(HAV68) for Algol, Fairchild's SYMBOL machine (RIC71) for manipulation, Abrams' APL string machine (ABR70), Melbourne and Pugmire's Fortran machine (MEL65), etc. These machine languages represent a broader class of languages than are conventionally considered (von Neumann) machine languages. shall refer to this broader class as Intermediate Machine Languages (IML). The tailoring of an IML to a specific higher level language is accomplished by incorporating instructions and data types in the IML which directly implement (i.e., mirror) the primitive operations of the higher level language. For instance, an ALGOL procedure call including the modification of the addressing environment is directly mirrored by the ENTER instruction in the B6500. Thus, instead of implementing the semantics of higher level language primitive operations through an unnecessarily long and complicated sequence of instructions (see Figure 1a), the IML is designed so that there is a single instruction or, at worst, a short sequence of instructions that efficiently carry out the primitive operation (see Figure 1b). by tailoring a machine language more closely to a Therefore. particular higher level language, the mapping between the higher level language and the machine language is simpler and results in a more compact and efficient generated code (MCK67). This trend should accelerate as the cost of software is recognized as the major cost component of a computer system (DEN71).

- \*The length of the line is intended to give some relative measure of the inherent computational activity involved in the execution of a statement or machine instruction.

- \*\*The sequence of machine instructions is intended to indicate the inefficient use of the computational activity of each instruction, and the high overhead of instruction fetching and decoding due to the large number of instructions required to be executed.

Figure 1. Mapping of a Higher Level Language to a Machine Language

4

The second trend, that is on the Processor-Memory-Switch level, has led to the development of computers that are able to carry out parallel activity at the functional unit level, instruction level, or process level. These different levels of parallel activity are exemplified by machines such as the CDC6600(TH064), which permits clocked asynchronous parallel operation of functional units, the ILLIAC-IV(SLO67), which permits lock-step execution of multiple copies of a single instruction stream on identical processors and the multiprocessor B825(AND62), which permits the execution of multiple asynchronous instruction streams on identical CPU's. This trend towards parallelism at the PMS level has occurred mainly in the design of high performance computer systems. However, as LSI technology brings down the cost of logic and as reliability of the computer system becomes an important component of the design, this trend toward parallelism should extend to many more types of computer systems (BEL72).

These two design trends on the ISP and PMS levels are not disparate but rather are separate aspects of a more general trend towards the design of complex problem oriented computers whose architecture departs considerably from a classical von Neumann architecture. The B6500, the ILLIAC-IV, and the SYMBOL machine represent to varying degrees an integration of these two trends in computer architecture. The B6500 configured as a multiprocessor system permits the allocation of multiple processors to the execution of a single Algol program, the ILLIAC-IV permits highly parallel

execution of problems involving an array structured data base, and the SYMBOL machine permits a set of non-identical processors to work in a parallel coroutine structure to interpret and execute a sophisticated IML instruction repetoire.

In parallel with these first two trends, there has been a third trend towards providing a systematic and flexible technique for implementing a processor in hardware. This third trend, that is on the Processor-Implementation-Technique level, has led to the to the development of the concept of a microcomputer (WIL69, HUS70), which provides a systematic and regular technique for specifying control at the circuit gate level. The major use, to date, of microcomputers has been in the implementation (emulation) of the processor of a specific type computer; e.g. IBM 360/40(IBM66), with the von Neumann microcomputer usually having a read-only control memory. there have been the beginnings of an attempt to combine complex microcomputer design problem-oriented computer design with (WEB67, ROS69), implementing a specific architecture by modifying the READ-WRITE control memory of the microcomputer. It is hoped that the goal of emulating a wide range of problem-oriented computers can be realized by dynamically modifying the control memory of a single This goal cannot be effectively attained on microcomputer system. microcomputers whose architecture is essentially designed for the emulation of the instruction set of a von Neumann type computer in a non-parallel PMS environment. This thesis offers an architecture for a microcomputer system that permits a systematic and flexible approach to the emulation of a wide variety of complex sequential and parallel intermediate machine languages in a dynamically varying PMS environment which contains multiple microprocessors and functional units.

## I.2.1 Traditional Microcomputer Architectures

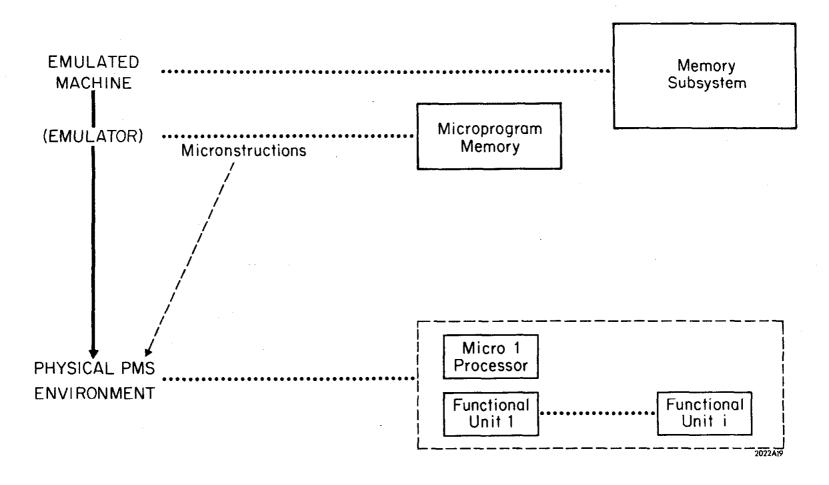

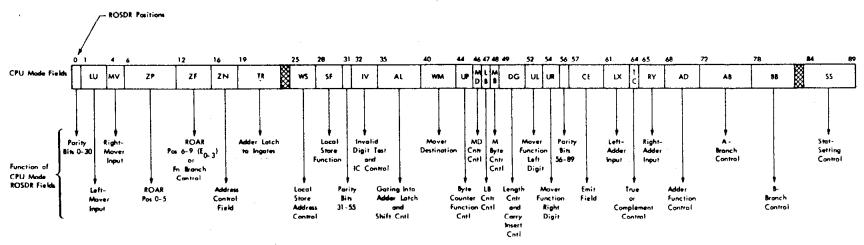

The conceptual architecture of a conventional microcomputer system is shown in Figure 2. The memory subsystem contains a machine language program (and its corresponding data) which is to be executed emulated computer. The microprogram memory contains microinstructions that are used to interpret instructions of the emulated computer. The formats of microinstructions on existing microcomputers can be characterized into two general classes: horizontal and vertical microinstruction formats (see Figure 3 and Figure 4 respectively). In a microinstruction specified in terms of the horizontal format, each bit of the microinstruction word controls a particular internal operation of the microprocessor (e.g., the opening or closing of a hardware data path between internal working registers, or the arithmetic operation to be performed on a data The vertical format microinstruction word is broken into a series of fields as in a conventional machine instruction, where each field is used to specify either one of a set of internal registers or of built-in arithmetic one operations. These microinstructions are executed on a single microprocessor which is connected to a set of functional units. The term functional unit is

used in a very broad context to refer to input/output devices, their corresponding controllers, and arithmetic units, such as a floating-point adder. In conventional microprocessors, the functional units connected are usually input/output devices or their corresponding controllers rather than arithmetic units.

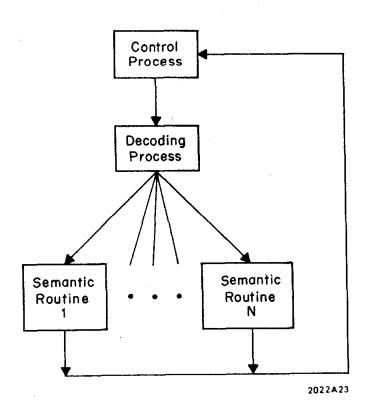

In order to perform an emulation using a conventional microcomputer architecture, the microprogrammer must first imbed the state image of the emulated computer, S(e), which includes the set of working registers of the computer (accumulator, index register, program counter, etc.) and its main memory into the state image of the microcomputer, S(m), which includes the Memory Subsystem and the internal state and working registers of the microprocessor. For efficiency, frequently accessed elements of S(e) (e.g. the program counter of the emulated machine, etc.) are stored, if possible, in the internal working registers of the microprocessor. An constructed out of microinstructions has a conceptual microprogram structure shown in Figure 5. The "control process" activates the "decoding process" with data that identifies the next instruction of the emulated computer to be executed; the decoding process then analyzes the instruction to be executed so as to determine the "semantic routine" together with its appropriate calling sequence, perform the semantics of the emulated whose activation will After the appropriate semantic routine been instruction. executed, the flow of control returns to the control process which, based on the results of executing the decoding process and

Figure 2. The Relationship between the Emulation Process and a Conventional Microcomputer Architecture

| Field | ROS Bits | Function of Field                          | <u>Field</u> | ROS Bits | Function of Field                           |

|-------|----------|--------------------------------------------|--------------|----------|---------------------------------------------|

|       | 0        | Parity of bits 0-30                        | LB           | 47       | LB counter control                          |

| LU    | 1-3      | Left input to mover                        | MB           | 48       | MB counter control                          |

| MV    | 4-5      | Right input to mover                       | DG           | 49-51    | Length counter and carry insertion control  |

| ΖP    | 6-11     | Bits 0-5 of next ROS address               | UL           | 52-53    | Mover function left digit                   |

| ZF    | 12 - 15  | Source of bits 6-9 of the next ROS address | UR           | 54-55    | Mover function right digit                  |

| ZN    | 16-18    | ROS addressing mode                        |              | 56       | Parity of bits 57-89                        |

| TR    | 19-23    | Destination of adder latch contents        | CE           | 57-60    | Emit field (used as data)                   |

|       | 24       | Spare                                      | LX           | 61-63    | Left input to adder                         |

| ws    | 25-27    | Source of local storage address            | TC           | 64       | True/complement control of left adder input |

| SF    | 28-30    | Local storage function                     | RY           | 65-67    | Right input to adder                        |

|       | 31       | Parity of bits 32-55                       | AD           | 68-71    | Adder function                              |

| IV    | 23-24    | Invalid digit test and instruction address | AB           | 72 - 77  | Condition branch test A                     |

|       |          | register control                           | [            |          | (furnishes bit 10 of next ROS address)      |

| AL    | 35 - 39  | Shift control and gating into adder latch  | ВВ           | 78-82    | Condition branch test B                     |

| WМ    | 40 - 43  | Mover destination                          | ļ            |          | (furnishes bit 11 of next ROS address)      |

| UP    | 44-45    | Byte counter function                      |              | 83       | Spa re                                      |

| MD    | 46       | MD counter control                         | SS           | 84-89    | Stat setting and miscellaneous control      |

Figure 3. Horizontal (minimal encoded) Microcode Format of IBM 360/50 (from HUS 70)

| Ο            | 4             | 8 1          | .2              | 16          |                       | 19   | 24         | 2        | ?7   | 31 |

|--------------|---------------|--------------|-----------------|-------------|-----------------------|------|------------|----------|------|----|

| GEAR<br>CODE | ARITH<br>CODE | MASK<br>ADRS | SHIFT<br>AMOUNT | C<br>L<br>R | T<br>E<br>S<br>T<br>A | OP A | B<br>O SEI | , I<br>B | OP B | R  |

| 0            | 4 6 7         | 7 8                    |   | 16       |   | 24                  | - 31 |

|--------------|---------------|------------------------|---|----------|---|---------------------|------|

| BRAT<br>CODE | TEST A MODE A | $\frac{B}{B}$ TEST BIT | A | TEST BIT | В | RELATIVE<br>ADDRESS |      |

Figure 4. Vertical (highly encoded) Microcode Format of MLP-900 (from LAW 71)

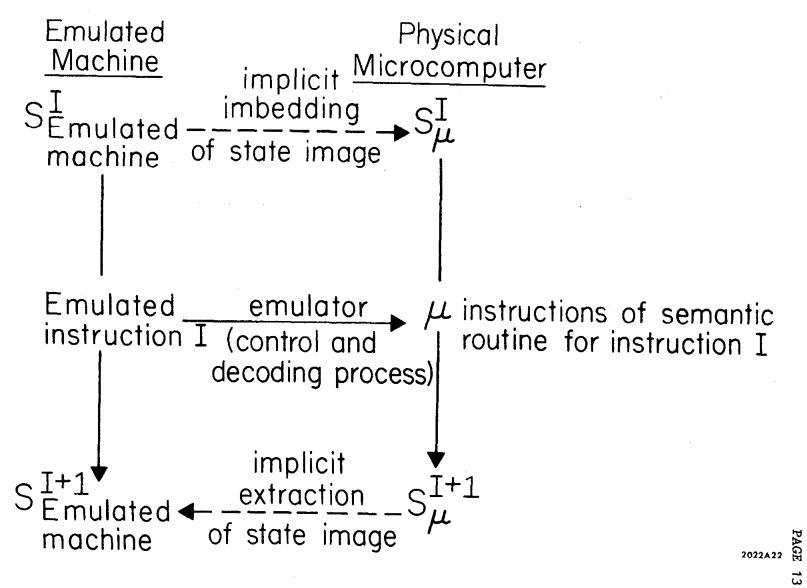

semantic routine, selects the next instruction to be emulated. This basic cycle is conventionally called (TUC65) the "Do Interpretive Loop" (DIL). This two step design process for an emulator is represented in terms of a commutative diagram in Figure 6\*.

# I.2.2 Basis for a New Microcomputer Architecture

In microcomputers designed to emulate a specific computer architecture, or family of computers with similar architectures, the imbedding of the state image is straightforward. There are internal registers dedicated to holding commonly accessed state information of the emulated computer. The control and decoding processes of the emulator are usually directly implemented in the hardware taking their data from the dedicated internal registers. This control and decoding hardware is usually directly integrated into the microprocessor's control structure used for the sequencing of microinstructions so as to create an extended control structure. Through this concept of an extended control structure, the sequencing of microinstructions is driven directly by the sequencing of emulated instructions. In addition, the internal data paths and microperations are tailored so as to make microprograms that carry out the semantic phase of an

<sup>\*</sup>The left hand side of the commutative diagram represents the effect of executing an instruction of the emulated computer on the state image of the emulated computer. The right hand side represents the sequence of transformations that the microcomputer must perform on its own state image in order to emulate this instruction.

Figure 5. Conceptual Program Structure of an Emulator

Figure 6. Commutative State Diagram of Conventional Emulation Process

emulation efficient and compact. Thus, a microcomputer is a flexible and efficient technique for emulating computers that have been anticipated.

However, this tailored microcomputer architecture is inefficient when used to emulate a machine language (IML) that is dissimilar in its instruction format, control structure or instruction semantics to the machine languages anticipated by the designer. This inefficiency occurs because:

- 1) the imbedding of the S(e) into S(m) is not straightforward (e.g., mapping a machine which has a 36 bit wide word into a microprocessor which has a 32 bit wide word) and dedicated (specific function) internal registers cannot be used directly to hold commonly accessed state information (TUC65);

- 2) the hardware implementation of the control and decoding processes cannot be used directly;

- 3) the microinstructions and the internal data paths they manipulate that were designed for a specific set of instruction semantics are clumsy when applied to the microprogramming of the control and decoding processes, and different instruction semantics.

These problems with a tailored microcomputer architecture are analogous in many respects to the previously discussed problems with the execution of higher level languages on a von Neuman machine.

In response to these problems with a conventional microcomputer architecture, new types of microcomputer architectures are beginning to be developed, most notably the QM-1 (ROS71) and MLP-900 (LAW71), which are designed more for general purpose emulation

rather than for implementation of a specific processor. These new microcomputer architectures differ from conventional architectures by providing the capability of configuring a set of non-specific internal of the microprocessor and their corresponding registers interconnection pattern into the specific configuration appropriate for the emulation of a particular IML. Once the particular configuration is set, the semantics of the microinstruction, when executed, operate directly in the context of the chosen configuration. This flexible configuration capability, referred to in less general contexts as residual control (FLY71), leads to ease of representation, code compactness, and efficient use of microprocessor resources\*. The concept of residual control represents a design trade-off between conventional microprocessors which are efficient but inflexible and non-specific microprocessor architectures which are flexible but inefficient because there is no specification of functions or internal resources for particular types of emulation. The cost of this capability for configurability is extra levels of hardware logic, and high speed memory to hold configuration specifications, which implies slower microprocessor cycle time, and thus a more costly microprocessor.

<sup>\*</sup>The concept of residual control represents the extraction from the microinstruction of the environmental information which remains static during the execution of a sequence of microinstructions. This environmental information specifies gating paths and adder configurations and modes, and is held in set-up registers which are used by the hardware to determine how to interpret a microinstruction.

This concept of dynamic reconfigurability for representational ease has also been employed in the design of other components of a computer system. In particular, the idea of virtual memory (DEN66) is directly analogous in its use and techniques for implementation to the idea of residual control. Both ideas represent attempts to match the structure of the computer system more closely (in this case, dynamically) to the structure of the problem to be programmed.

microcomputer, The conventional augmented with the capability for dynamic configuration of bus interaction patterns and for generalized bit string extraction and (i.e., QM-1)manipulation (i.e., MLP-900, B1700(WIL72)), provides an appropriate environment for emulating a wide range of machine languages which have simple control structures and instruction semantics that operate on simple data structures (e.g. von Neuman type computers). intermediate machine languages that are tailored for the execution of higher level languages or for the execution of operating system implementation languages are not so simple since the complexity of the higher level language operations is reflected in the semantics of the IML instructions and control structure. If the current trend in the development of higher level languages is maintained, language-oriented IML's will employ increasingly more sophisticated control structures, such as recursion, coroutines, parallelism, etc., and instructions that access complex data structures, such as lists, trees, arrays, etc., and perform operations such as sort (LEV72) matrix manipulation (GRA70, ABR70), etc. As will be argued below, these IML's call for a more sophisticated control structure in the microcomputer.

The control structure of a machine language or higher level language consists of a set of control rules(CR) and a data structure for control(CDS) commonly called Program Status Word(PSW) or processor state, on which the control rules operate. The control rules determine at each meaningful unit of activity of the language which statement or statements of the language will next be executed. For example, if the CDS of a simplified computer consisted of a program counter and an interrupt register, then the CR of this simplified computer might be the following paradigm: if there are no interrupts pending, then execute the instruction at the location specified by the program counter, otherwise, store the program counter at a fixed location in the program memory, reset the interrupt flip-flop, place the address of the interrupt handling routine in the program counter, and then execute the first instruction of the interrupt handling routine. This definition of a control structure makes a clear distinction between the control structure of a language and the execution of control statements of a language, e.g., conditional branch instructions, etc. The control statements of a language implicitly, rather than explicitly, affect sequencing by modifying only one part of the control structure, namely, the CDS; the actual sequencing of statements occurs only by the interpretation of the control data structure by the control rules. For example, consider the results of executing the control statement "BRANCH TO LOCATION X" in terms of the control structure of the simplified computer discussed previously. The branch statement, when executed, places the address X in the program counter; however, the next instruction to be executed may not be at address X since during the time the branch instruction was executed an interrupt could have occurred.

The simple sequential control structure of a conventional microcomputer is inappropriate for emulation of sophisticated IML's in a parallel PMS environment for the following reasons:

- 1) The control structure component of the state image of sophisticated IML's is not easily imbedded in the control structure component of S(m); in particular, all parallel activity specified in the control structure component of S(e) must be sequentialized when imbedded in the control structure component of S(m); in essence, if the emulated machine contains instructions capable of fork-join type parallelism(CON68), there should be a simple and short sequence of microinstructions that modify control structure components of S(m) so that the microcomputer system will directly start to emulate in parallel the newly created instruction stream defined by the fork instruction.

- 2) The control structure for sequencing the different phases (tasks) required in the emulation of sophisticated IML's may not be sequential: the instruction decode, and fetch, and semantics phases may be pipelined, as in the 360/91(AND67), or the phases may interact in a parallel or quasi-parallel coroutine as in the SYMBOL machine.

- 3) The control structure may be required to represent the coordination, on a very fine interaction level, of multiple microprocessors and functional units, such as the lock-step execution of processors in the ILLIAC-IV, or scheduling of asynchronous functional units in the CDC-6600.

Thus, the flexibility of the control structure of the microcomputer is crucial to the effective emulation of sophisticated IML's. In particular, the control structure of a microcomputer should be able to be dynamically restructured, in a manner similar to but more general

than the reconfigurability specified through residual control and virtual memory, so that it more directly mirrors the control structure of the emulated machine and its emulator.

#### I.2.3 A New Microcomputer Architecture

The microcomputer architecture to be presented in this thesis is based on unifying in a single framework the concepts of residual control, virtual memory, and dynamic (restructurable) control structure. These concepts have been integrated through the idea of a virtual PMS environment; this idea embodies the capability for reconfiguring both the internal and the external environment of a microcomputer system. The concept of residual control as used in this context allows the varying of the number of internal working registers of each microprocessor; the concept of virtual memory in this context allows the varying of the structure of memory, e.g., its size and word length; the concept of a dynamic control structure allows the varying of the number of microprocessors and functional units, their interconnections and interaction patterns.

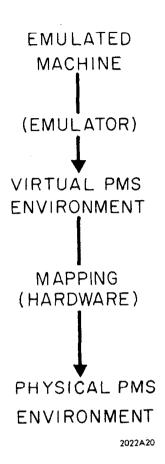

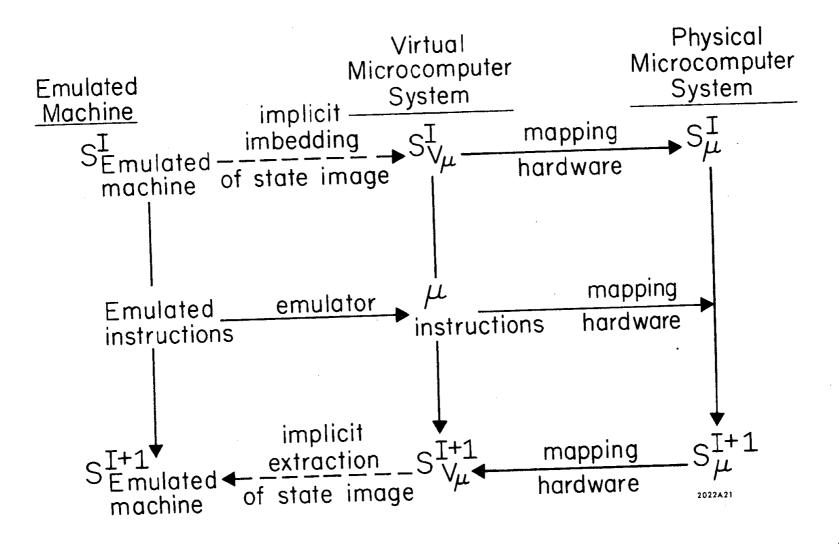

The concept of a virtual PMS environment leads to a new view of emulation pictured in Figure 7a and 7b, where S(vm) represents the virtual state image of the microcomputer system created through the specification of a particular PMS environment and the additional level of hardware is used to map microoperations, performed in the context of the virtual PMS environment, onto the actual (physical) PMS

environment. This additional level of hardware is analogous to the hardware in a virtual memory system which manages the page tables and performs the mapping of virtual addresses to physical addresses. The extra dimension of representational freedom provided by the concept of a virtual PMS environment allows:

- 1) The virtual state image of the microcomputer system, S(vm), to be structured so as to make the imbedding of the state image of complex IML's, S(e), straightforward;

- 2) The microinstructions to operate directly in the context of an appropriate S(vm) so as to make the coding of the emulator compact and simple;

- 3) The emulator to be coded so as to be independent of the physical PMS environment but, at the same time, exploit physical resources when available.

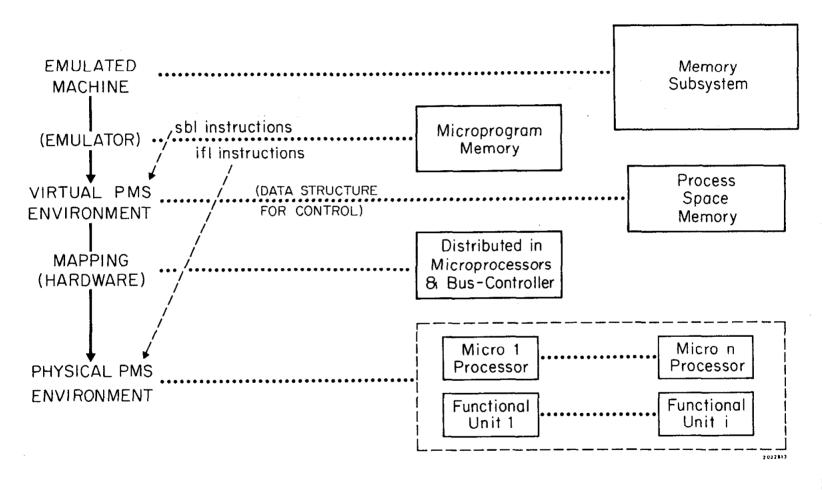

The concept of a virtual PMS environment also leads to a new view, as pictured in Figure 8, of a microcomputer architecture. this new architecture, there are two distinct hardware levels of control that are structured in a hierarchical fashion: the conventional level of control, contained in each microprocessor, for the sequencing of microinstructions, and a new level of control for the sequencing of microprocessors and functional units; thus, the microcomputer system contains both local. distributed structures and a global, system-wide control structure. The control rules for this new level of control are implemented in hardware which is distributed in each microprocessor and in the controller for the bus(ses) which are used for inter-processor communication. This new level of control must be an integral part of the hardware organization for reasons which are analogous to the use of special mapping hardware

Figure 7a. A New View of Emulation Process

Figure 7b. A New View of Commutative State Diagram of Emulation Process

for virtual addressing. Otherwise, the overhead in implementing highly structured parallel interaction patterns\*, where the parallel activity is of short duration, will overwhelm the inherent parallelism of the interaction patterns. The control data structure for this new level of control is contained in a separate memory called the Process Space Memory (M.PSM).

A particular virtual PMS environment is dynamically defined by constructing an appropriate global control structure for the microcomputer system. An appropriate global control structure is constructed by dynamically modifying the syntax, i.e., the number of data elements and their relationships, of the control data structure (CDS) contained in the Process Space Memory. In a conventional computer or microcomputer system, the data structure for control contains a fixed set of data elements whose relationships are predefined. Thus, in a conventional system, control can only be modified by changing the value of data elements in the CDS. The ability added here to modify the syntax of the data structure for control, as will be seen later, is the key to tailoring a virtual PMS environment for a particular emulated machine.

<sup>\*</sup>A highly structured interaction pattern among microprocesses implies that there is a high degree of coordination among microprocesses. This is in contrast to an unstructured interaction pattern which implies that once one microprocess has initiated the activity of another microprocess, there is no further coordination of the activity of these two microprocesses.

Figure 8. A New View of Relationship between Emulation Process and Microcomputer Architecture

There are two general classes of microinstructions in the microcomputer. One class, called the Integer Function Language (IFL), deals with internal registers of the microprocessor, and are like conventional vertical microinstructions. The other class, called the Structure Building Language (SBL), deals with the external environment of the microprocessor by modifying the CDS contained in the Process Space Memory. The SBL can be thought of as a control structure definitional language which is designed so as to regularize control at the microprocessor/microprocessor interaction level. microprocessor/functional unit interaction leve1 and microprocessor/Memory Subsystem interaction level.

This new level of hardware control can also be thought of as a simple, hardware operating system which controls the scheduling and interactions among microprocessors and functional units. In this context, the CDS stored in the Process Space Memory (M.PSM) is the control blocks and queues that describe the interaction and existence of tasks (or processes) in a multiprogrammed operating system. The SBL statements are analogous to requests for supervisor services that affect interprocess interaction patterns in such an operating system. The SBL can manipulate and build up the CDS only in ways understandable to the global control rules of the microcomputer system; the CDS, in a very general sense, can be considered a control structure definition program which, when interpreted by the global control rules of the microcomputer system, defines a particular sequential or parallel control structure for sequencing of virtual microprocessors (microprocesses\*) and functional

units. The CDS can also be thought of as a variable structure template that defines a particular internal and external structure for the microcomputer system, thus the idea of a virtual PMS environment. An SBL program is quite different from a sequence of control statements since the control structure definition program (the CDS), constructed by the SBL, is external to the microprogram. The separation of the control structure definition program permits the static parts of the virtual PMS environment to be generated only once for repeated executions of emulation.

SBL statements dynamically modify the CDS to directly reflect the state transitions occurring in the emulated computer. SBL statements reflect these state transitions by modifying the CDS so as to change: 1) the data environment of a microprocess, 2) the activity state of a microprocess, or 3) the interaction patterns among microprocesses (only this third case results in a modification of the syntax of the CDS). The CDS explicitly represents the relationship between the execution of a microprogram and the immediate data environment (parameters) in which the instructions of the microprogram operate. This relationship between the control and data environments, as will be seen in more detail later, allows 1) the representation of data environment interrelationships among microprocesses, and 2) the state of the emulated computer to be integrated directly into the CDS (e.g., the IML program counter could be a parameter of a microprocess

<sup>\*</sup>The relationship between a microprogram and microprocess is analogous to the relationship between a program and a process(LAM68).

defined in the CDS). Thus, an IML control statement, such as a conditional branch in a pipelined emulator, can be implemented by an SBL microinstruction that modifies the data environment (e.g., the IML program counter parameter) of the microprocess that asynchronously fetches the next instruction to be executed. Likewise, the processing of an IML interrupt can be handled by an SBL instruction that suspends the activity of the microprocess that emulates the IML interrupt handling process. IML control statements that specify the creation of new paths of controls (e.g., fork-join instruction , etc.) can be implemented by an SBL statement that builds up the appropriate structure in the CDS for emulating IML instructions along this newly created control path. Additionally, the SBL can be used to construct in the CDS: 1) control structures for sequencing microprocesses which carry out the semantics of emulated instructions, 2) control structures for I/O, and 3) control structures for data accessing operations.

#### I.3 An Outline of the Justification for This

New Microcomputer Architecture

The remainder of the thesis will develop the following conclusions:

<sup>1)</sup> The concept of a virtual PMS provides a representational framework in which a wide variety of sequential and parallel control structures can be easily expressed.

<sup>2)</sup> The SBL can be used to simply and compactly code emulators for complex IML's.

3) A computer organization which implements the concept of a virtual PMS can be designed such that highly parallel activity specified on the virutal PMS can be translated without undue overhead into highly parallel activity on the physical PMS.

Chapter II contains a detailed discussion of the SBL and the associated global control structure, and their applicability for representing particular types of control structures.

Chapter III reviews in a step by step manner the design and coding of an emulator for a complex IML. The emulator for this complex IML represents a comprehensive test case that is used to illustrate how control structure concepts, such as distributed control, pipelining and recursion are coded in the SBL.

Chapter IV discusses the computer organizational issues involved in implementing this proposed microcomputer architecture. Specifically, the following organizational issues will be discussed:

- 1) the bussing structures to access memory, and for interprocessor communication;

- 2) the hardware algorithm for scheduling of virtual microprocessors on actual microprocessors.

- 3) the design requirements necessary to insure no hardware deadlocks are introduced which are not already present as software deadlocks.

- 4) the issues involved in the use of a memory cache per microprocessor.

- 5) the internal microprocessor organization necessary to implement the concept of a virtual microprocessor.

Chapter V contains an evaluation of the performance capability of a possible hardware implementation of this microcomputer architecture when executing the emulator discussed in Chapter III. This evaluation is based on statistics produced from a detailed hardware simulator which permits the varying of hardware parameters, such as the number of microprocessors, the number of busses, the interleaving of memory, the size of the cache, and the cycle times of a microprocessor, memory, or cache. This evaluation will attempt to indicate the crucial parameters that affect systems performance. Finally, Chapter VI summarizes the major results of the thesis.

#### II. Structure Building Language (SBL)

and

the Data Structure for Control (CDS)

## II.1 Motivation and Important Design Considerations

The design of the SBL and its associated data structure for control is based on the view that complex emulators can be best expressed in terms of a set of (virtual) microprocessors that interact in a highly structured manner. Further, these highly structured interaction patterns (e.g., a virtual PMS environment) are different for different types of emulators. This view represents a modular, task oriented approach to managing the complexity of emulation, which is, in fact, the technique used to design sophisticated computer organizations such as the IBM 360/91, CDC 6600, BCC-500(LAM70) and the SYMBOL machine.

The CDS has been defined so as to (1) allow the flexible structuring of a virtual PMS environment, and (2) insure that the hardware algorithm for the mapping of virtual microprocessor activity to actual microprocessor activity is straightforward. The SBL microinstructions are not oriented toward specifying any particular method of microprocessor interaction patterns, but rather are building blocks on which different interaction patterns can be defined. For

example, Dijkstra's semaphore (DIJ65), Saltzer's wakeup-waiting switch (SAL66) and message-queuing (SAA70,RID71) are all communication emulated by a short sequence of SBL patterns that can Ъe microinstructions. However, SBL microinstructions are of sufficient complexity so as to provide information to the hardware mapping algorithm which allows the mapping algorithm to take advantage of similarities between the structure of the virtual PMS environment and that of the actual PMS environment. For instance, if it is desired to broadcast the same data to 64 virtual microprocessors and there are at least 64 actual microprocessors, then the mapping algorithm should be able broadcast the data directly in one step to all 64 microprocessors, rather than sequentially transferring the data to each microprocessor.

The remainder of this chapter is divided into three sections: the Data Structure for Control, the Structure Building Language, and the Generation of the Data Structure for Control. The first section, on the CDS, describes the syntax of microprocess interaction patterns, e.g., "how" microprocesses can communicate and with "whom" they can communicate. The second section, on the SBL, describes the semantics of microprocess interaction patterns, e.g., "how" and "when" different syntactically defined interaction patterns are invoked. The third section, on the generation of the CDS by the SBL, describes how different syntactic interaction patterns are dynamically constructed.

### II.2 Data Structure for Control (CDS)

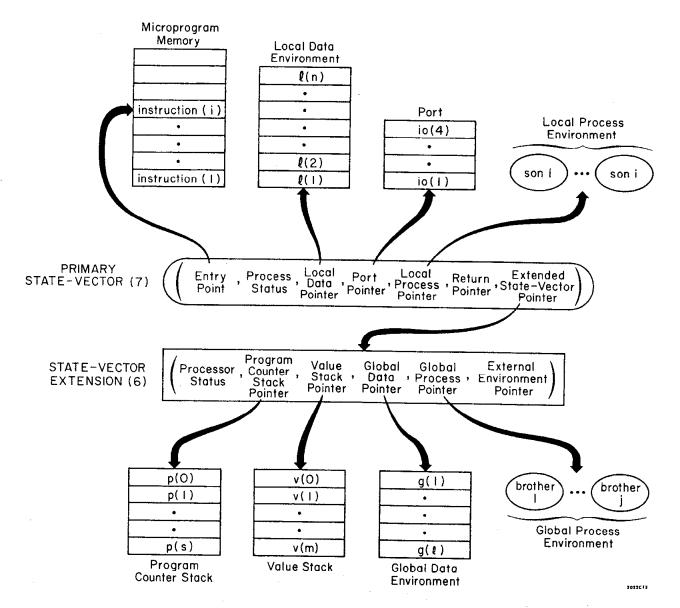

The CDS defines the syntax of microprocess interconnection and interaction patterns. The CDS consists of an arbitrary number of microprocess state vectors (MSV); each MSV has a structure, pictured in Figure 9a, which has 13 components; different microprocess interaction patterns are defined by varying the number of state vectors and the values their components. Changing the values of MSV components, as will be seen shortly, changes the relationship among microprocesses.

A microprocess state vector is contained in two disjoint structures, a primary state vector (PMSV) having 7 components, and a state vector extension (EPSV) containing 6 components; these two disjoint structures are connected by a state vector extension pointer contained as a component of the primary state vector. The MSV is separated into two structures so as to allow the sharing of state vector extensions among microprocesses; the sharing of a state vector extension by two or more microprocesses defines a FORTRAN subroutine type control structure, i.e., each microprocess has its own local statically assigned storage and common storage area for communication with other microprocesses. In addition, this separation allows the global environment within which a microprocess executes to be changed with the modification of a single pointer, i.e., the state vector extension pointer. One of the methods for microprocesses to interact is for the initiating microprocess to change the state vector

Figure 9a. Structure of Microprocess State Vector

extension pointer of the microprocess to be activated, as will be discussed more fully in the next section.

The remaining components of the microprocess state vector (MSV), for purposes of explanation, can be broken into two overlapping classes: external-environment components and internal-environment Each of these classes can be further subdivided into control-environment components and data-environment components. external control-environment components define the of set microprocesses that a microprocess can directly communicate with. external data-environment components define how other microprocesses can transfer data to a microprocess. The internal control-environment components define the loca1 CDS for the sequencing microinstructions of a microprocess. The internal data environment components define the internal working registers of the microprocess. Figure 9b contains a diagram of this categorization of the components of a MSV.

The values of the components of an MSV are integers, pointers to MSV's, or pointers to registers that contain descriptors of either an array of registers or an array of MSV's. The Process Space Memory holds the collection of MSV's that define the CDS as well as the registers pointed to by components of the MSV's. The MSV, together with the registers it points to, define the state image of a virtual microprocessor S(vm).

Figure 9b. Functional Classification of Microprocess State Vector Components

### II.2.1 External Control Environment

There are four external control-environment components contained in an MSV: a local process environment pointer, a global process environment pointer, an extended environment pointer, and a The first three of these configure the CDS in terms return pointer. of a tree of microprocesses. In this context of a tree of microprocess state vectors, the local process environment component specifies a set of son MSV's, the global process environment component specifies a set of brother MSV's, and the external environment component specifies the father MSV. The external environment pointer provides a mechanism for tracing back up the tree so as to allow communication with the global process environment of the father, grandfather, great grandfather microprocesses, etc. The external environment pointer thus allows the nested structuring of control environments.

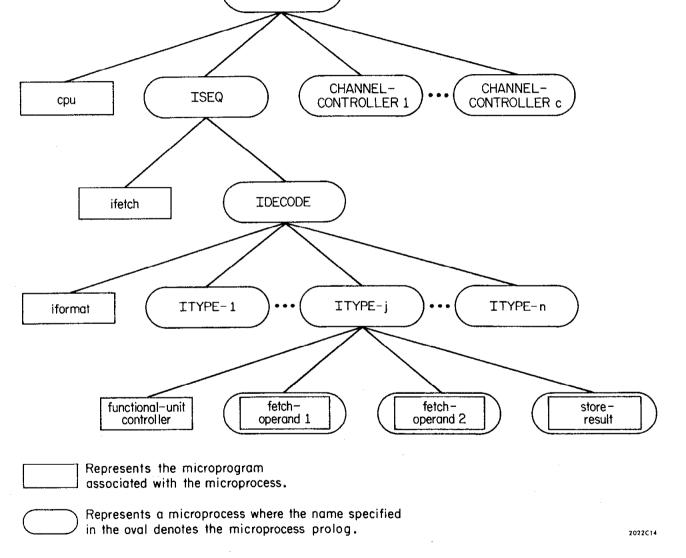

> Example 1: Consider the design of an emulator which works in a pipelined manner. In this pipelined emulator, there are separate, asynchronous microprocesses for fetching, decoding and carrying out the semantics instructions, for fetching and storing operands, and for controlling I/O channels. A possible CDS for this pipelined emulator is pictured in Figure 10. The microprocess computer controls the Channel-Controller microprocesses, and pipelined instruction emulator. The microprocess ISEQ (Instruction SEQuencer), IDECODE, and ITYPE-j implement, respectively, the control, decoding, and semantic processes of the pipelined emulator.

The tree of microprocesses constructed by the first three components represents static control linkages among microprocesses, whereas the

COMPUTER

Figure 10. Control Data Structure for a Pipelined Emulator of a Conventional Computer

PAGE 37

return pointer component represents a dynamic control linkage. These static control linkages provide a syntactic framework for the specification of dynamic sequencing among microprocesses, whereas the return pointer provides a means for specifying a dynamic control connection between the initiating and initiated microprocesses.

The CDS is in the form of a tree in order to easily specify concepts such as hierarchical structure (functional control recursion. decomposition), parallelism, coroutines, and Representation of hierarchical structure and recursion is possible because additional levels may be dynamically built in the tree by filling in the local process environment component of the MSV. Representation of parallel and coroutine structures is possible because brother MSV's in the tree may be treated as distinct, independent processes, each with its own state information. addition, a set of brother microprocesses is a convenient framework for specifying multiple activation patterns, e.g., the 64 Processing Elements (PE) of an ILLIAC-IV can be thought of as a set of brothers which are executed together. Brother MSV's are stored in consecutive locations in the Process Space Memory. This method of storing brothers permits any brother to be accessed in one M.PSM memory reference\*.

<sup>\*</sup>An arbitrary size block of MSV's can be specified in terms of three parameters: the beginning of the array of MSV's, the starting address in the array, and the length of the subarray. This concise representation of a block of MSV's could be possibly used to implement efficiently a hardware broadcast operation.

A tree data structure is also a convenient syntax framework (using father, son, and brother relationships among MSV's) for defining distributed control systems. The control structure of a complex system can sometimes be conveniently represented through a hierarchical structure where in each sibling set (or structural level) of the tree there is embedded a simple control rule (via a clocking process) (HOR69) that initiates the sequencing of microprocesses. If additional clocking processes are contained in the sibling set, control may pass to these son microprocesses after initialization. Thus, instead of one complex control rule for the entire system, the control can be distributed throughout the system. In addition, since the control rules can be coded such that their addressing structure is not based on their absolute locations in the tree, but only on their relative position in the tree, a single microprogram could be used by clocking processes throughout the tree.

A distributed control structure can be used to define, depending upon the number of clocking processes that are simultaneously executed, either quasi-parallel (DAH66) or parallel control structures. Further, many sequential control structures can also be easily defined in terms of a quasi-parallel control structure. For example, a subroutine call mechanism can be considered a quasi parallel control structure (BIN69): the execution of the subroutine call suspends the activity of the caller and activates the called subroutine; the return from the subroutine then terminates the activity of the subroutine and reactivates the caller. The block

structure and procedure calls of Algol and coroutines are other examples of sequential distributed control structures. In essence, the tree structure of the CDS allows the structure of a complex process to be functionally decomposed into a set of executions of less complex processes.

#### II.2.2 External Data Environment

There are four external data-environment pointers contained in a MSV: a port pointer, a global data environment pointer, a value stack pointer, and an external environment pointer. The port component, which specifies a block of up to four registers, allows the transfer of data to a microprocess to occur at the same time the addition. the communicating is activated. In microprocess microprocess does not have to know the location or structure of the The concept of a port allows for the construction of port. communication patterns where there are many possible microprocesses that may communicate and their sequence of communication is undefined. This type of communication pattern commonly occurs when a microprocess synchronizing (clocking) process for asynchronously acts communicating microprocess e.g., Dijkstra semaphores, message queuing, etc. The port component may also be used to define broadcast control structure, e.g., multiple microprocesses having the same port.

The global data environment component, which specifies a block of registers of arbitrary length, allows the transfer of data to

a microprocess to be separated from the activation of that microprocess. This type of communication pattern generally is used when 1) there are many microprocesses that access a single global data base, and 2) the values of the data base cannot be simultaneously modified by multiple microprocesses nor when other microprocesses are accessing those values.

The value stack component allows two microprocesses to communicate in a coroutine manner. This coroutine communication pattern is defined by setting the value stack components of the MSV's of both microprocessors to the same value.

The external environment pointer component, which points to an MSV, provides a mechanism for accessing the global data environments of a nested structure of microprocesses. This ability to define a nested structure of data environments is very useful in defining Algol-like (block) control structures.

Example 2: Consider the pipelined emulator discussed in example 1. The microprocesses that make up this emulator could be structured so as to communicate with each other in two ways. One communication pattern is through a shared global data base where the frequently accessed data elements of the state image of the emulated computer are held. other communication pattern is through the ports of each microprocessor. In particular, the microprocess, ISEQ, that asynchronusly fetches instructions transmits the fetched instructions. to the microprocess, IDECODE, through IDECODE's port. IDECODE, as will be discussed in more detail later, can define when a communication through its port from ISEQ will be consummated. In this way, the ISEQ microprocess does not have to worry about whether the IDECODE microprocess has already decoded the previously fetched instruction. However, if the fetched instruction was transmitted to the IDECODE microprocess through the shared global data base then some explicit interlock mechanism would be needed to guarantee that IDECODE has already decoded the previously fetched instruction.

#### II.2.3 Internal Control Environment

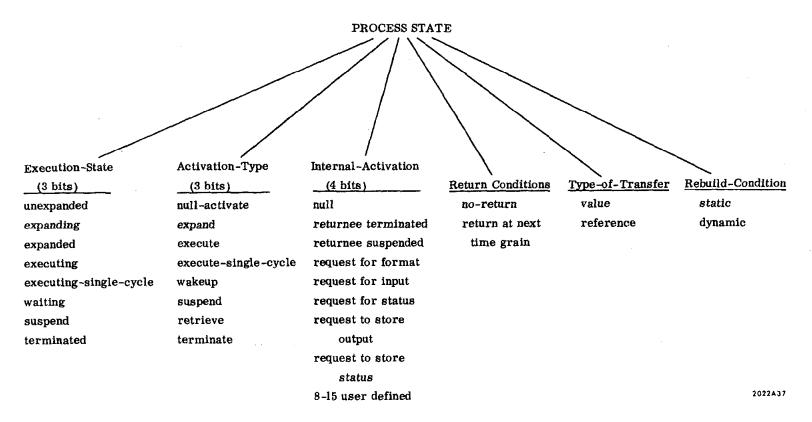

There are four internal control-environment components contained in an MSV: an entry point component, a process status component, a processor status component, and a program counter stack. These four components define the microprocessor state. The entry point component specifies the beginning address of the microprogram that will be invoked when the microprocess is executed; the process status component specifies the execution status of the microprocess, and the activation-type requested of the microprocess (the process status will be discussed in detail in the next section); the processor status component specifies the internal status of the microprocessor, e.g., the condition code of the last arithmetic result; the program counter stack component specifies a block of registers that will be used as a stack to hold the microprocessor program counter when the microprocess is suspended or when a microprogram subroutine is invoked.

#### II.2.4 Internal Data Environment

The remaining set of internal environment components defines the internal working registers of the microprocessor. The internal data environment is specified in terms of two components: a local

data environment component, and a value stack component. The local data environment component specifies a block of registers that can be directly addressed by a microinstruction. The local data environment is often used to hold data items that are not modified over repeated executions of the microprocess. Thus, it serves a function similar to the "STATIC VARIABLES" of a PL/I procedure. The value stack component specifies a block of registers that will be used as a stack to hold temporary results that are generated by the execution of microinstructions.

## II.3 Structure Building Language (SBL)

The SBL consists eight of different types microinstructions, as summarized in Table 1\*. The SBL has two a syntactic function and a semantic function. functions: the syntactic function involves the dynamic construction of the CDS discussed in the previous section, while the semantic function involves the dynamic invocation of microprocess interaction patterns defined in the CDS. In essence, the syntactic microinstructions dynamically define static, time-independent interrelationships among

<sup>\*</sup>In the original formulation of the SBL discussed in (LES69), there was an additional SBL semantic microinstruction: SCP (Sequential Clocking Process) which was designed to iteratively activate an array of microprocess to simulate the effect of a sequential, parallel or overlap FOR statement. This SBL statement was removed because, through a combination of ASP, SEL and IFL microinstructions, the function of SCP statement could be easily implemented without significant affect in code density nor execution speed.

microprocesses. Whereas the semantic microinstructions use these syntactic interrelationships among microprocesses as a convenient representational framework within which define to dynamic, time-dependent interrelationships among microprocesses. The semantic microinstructions are similar in function to the control statements of conventional computer since both implement different control structures by modifying values of data elements of CDS; except, the semantic microinstructions operate in the context of CDS which can be dynamically restructured.

There is a clear distinction in the SBL between syntactic and semantic operations. This clear distinction allows semantic operations to be clearly divorced from syntactic modifications to the CDS. As will be discussed more fully in the next section, this divorce permits syntactic modification to the CDS to be generated only when absolutely necessary.

Example 3: Consider the CDS for an IML emulator which allows fork-join type parallelism. The CDS for this emulator can be structured in two possible ways. is to dynamically generate in the CDS an appropriate syntactic structure to interpret a new stream of emulated instructions every time a fork operation emulated. The other approach is to allow only a fixed number of fork operations to be invoked at any one time; thus, a static syntactic structure can be generated, when the CDS for the emulator is initially constructed, that permits the interpretation of up to some fixed number of emulated instruction streams. In either of approaches, the same set of semantic operations can be employed because of the clear separation of syntactic generation from semantic operations.

The microinstructions under the category "Structure Building" in Table

1 are classified as syntactic microinstructions while the remaining

## Single Microprocess Activation:

ASP (Activation and Synchronization Clocking Process) a general mechanism for coordinating the activity of two microprocesses;

### Multiple Microprocess Activation:

SEL (Selection and Broadcast Clocking Process) activates in a broadcast manner an array of microprocesses;

## Functional-Unit/Microprocess Interaction:

FCP (Functional -Unit Clocking Process) coordinated activity of functional unit with microprocesses that generates the inputs and stores the outputs of the functional unit;

# Memory/Processor Interaction:

<u>MEM</u> (Memory Clocking Process) fetches (or stores) a bit-string from memory-subsystem into the micro-process port.

## Microprogram Invocation:

MSC (Microprogram Subroutine Call) defines the parameters for a subroutine call and then executes this call;

# Structure Building:

GEN-PMSV allocates and initializes an array of primary microprocess state vectors;

GEN-EPSV allocates and initializes an extended microprocess state vector;

GEN-REG allocates a block of registers or creates a descriptor to a subarray of registers.

2022A36

microinstructions type are classified as semantic microinstructions.

The syntactic microinstructions will be discussed in the next section.

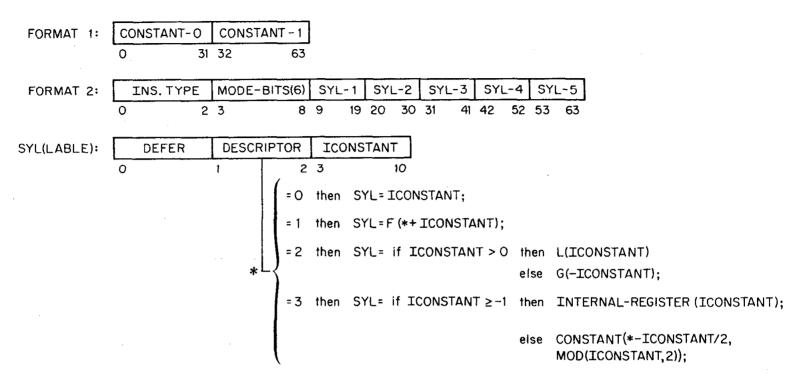

The same microinstruction internal representation is used for all SBL microinstruction types and is pictured in Figure 11. Each microinstruction word contains six mode bits and five syllables. The execution of SBL microinstructions has two phases: 1) the evaluation of the five syllables, and 2) the execution of a specific control or structure building operation based on the instruction type, computed syllable values and mode bits\*.

There are three dimensions to the specifications of dynamic interaction patterns among microprocesses: "when", "who", and "how". The "when" dimension, which has not been discussed up to now since it has no syntactic component, specifies at what time points in the activity life of a microprocess can certain types of communications be received. The "when" dimension is an integral part of the specification of highly structured interaction patterns; this is especially true since 1) the built-in communication mechanism is primitive, e.g., no message queuing, and 2) it is desired to be able

<sup>\*</sup>The SBL microinstructions have been referred to in a previous paper (LES71) as SBL macros because of their two phase execution cycle. In this context, the microinstruction type can be considered to define a control structure definitional template (prototype) that is expanded, based on the values of the syllables of a microinstruction, when a microinstruction is executed. The specification of particular values for the parameters of the template then defines a particular instance of a basic control rule or structure building operator.

<sup>\*</sup>A SYLLABLE CAN BE EVALUATED IN FOUR WAYS DEPENDING UPON THE VALUE OF THE DESCRIPTOR.

THE FOUR WAYS ARE: (O) AN IMMEDIATE DATA ITEM; (1) THE RESULT OF A CALL TO A MICROPROGRAM FUNCTION; (2) THE VALUE OF A REGISTER OF THE LOCAL, OR THE GLOBAL DATA ENVIRONMENT OF THE MICROPROCESS; OR (3) THE VALUE OF AN INTERNAL STATE REGISTER OR A CONSTANT STORED IN THE MICROPROGRAM MEMORY.

to emulate many different types of communication patterns. The "when" dimension is based on the execution-state of the microprocess that is communication, and the type of communication (activation-type) desired by the microprocess that is to initiate the communication. The set of possible execution states represent the different phases in the life cycle of a microprocess. The semantics of SBL microinstructions are defined so that communication between two microprocesses is only consummated when the execution-state and type of communication (activation-type) are agreeable for communication\*. The agreeable states are specified in Table 2. The set of agreeable states is designed so that a microprocess can 1) sequentially accept and process multiple communications, 2) selectively accept only certain types of communications, and 3) asynchronously accept requests for communication.