SLAC - PUB - 3467 October 1984 (1/A)

# DESIGN AND PERFORMANCE OF THE STANFORD LINEAR COLLIDER CONTROL SYSTEM

# R. E. MELEN

Stanford Linear Accelerator Center, Stanford University, Stanford, CA 84805

## Abstract

The success of the Stanford Linear Collider (SLC) will be dependent upon the implementation of a very large advanced computer-based instrumentation and control system. This paper describes the architectural design of this system as well as a critique of its performance. This critique is based on experience obtained from its use in the control and monitoring of 1/3 of the SLAC linac and in support of an extensive experimental machine physics experimental program.

#### 1. Introduction

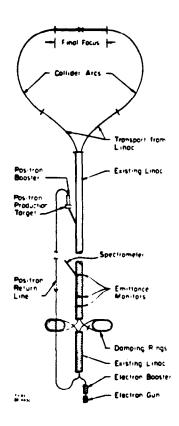

The SLAC Linear Collider<sup>1</sup> (SLC) project will provide electron-positron colliding beams at a center-of-mass energy of 100 GeV with a luminosity in excess of 10  $^{30}$  cm<sup>-2</sup>sec<sup>-1</sup>. The SLC general layout in Fig. 1 shows how the existing SLAC 2 mile linac will be combined with several additional accelerator components to produce colliding beams.

An accelerator cycle will begin with the assumption that the electron and positron damping rings each contain two equally spaced high-intensity low-energy bunches. One of the positron bunches will be extracted from the damping ring, passed through a bunch-length compressor, and injected into the linac. Then both electron bunches will be extracted from the electron damping ring, passed through a bunch-length compressor, and injected into the linac. The typical spacing of the three bunches in the linac will be about 15 meters.

The three bunches will be accelerated along the linac. The third bunch, an electron bunch, will be extracted from the linac at the two-thirds point and directed at a positron production target. The first two bunches, a positron bunch followed by an electron bunch, will continue to the end of the 2 mile linac where they will have attained an energy as high as 50 GeV. At the end of the linac, the two bunches will be separated by a DC magnet and each will then pass through approximately 4000 feet of matching transport, collider arc, and a final focusing section, before colliding at the interaction point.

In the mean-time, the positrons produced by the third "scavenger" electron pulse will be focused and accelerated and then brought back to the beginning of the linac. These positrons will then be accelerated through the first linac sector and injected into the positron damping ring to replace the positron bunch that was previously ejected. Then two bunches of electrons, created by the electron gun and electron booster, will be accelerated through the first linac sector and injected into the electron damping ring to replace the two electron bunches previously-ejected. The following cycles will continue in the same manner with the positron bunch, that is extracted then replaced, alternating between the two positron damping ring bunches.

#### Fig. 1. Layout of the SLAC Linear Collider.

The purpose of the SLC Instrumentation and Control (1&C) system is to produce the appropriate monitoring and control functions to successfully direct the complex SLC operation described above in order to deliver two reliable low-emittance beams to the collision point. The system must also provide a quick and efficient means of switching between SLC operation and other linac operations, such as delivery of beams to the experimental yard and the filling of the SPEAR and PEP storage rings.

The first chore for the control system is to provide an efficient and flexible means for setting up the thousands of devices which affect the beam parameters. Then the system must monitor the beam parameters and make appropriate corrections to the initial settings. Finally, the system must monitor the health of all components and automatically correct for inoperative devices, if possible, or at least notify the machine operators of a failure.

The SLC I&C task is especially demanding because of the tight beam-tolerance requirements and the very large number of unique devices that affect the beam. Further, the control system must not only work flawlessly, but it must simultaneously allow for the rapid development and testing of new or upgraded

1

Invited paper presented at the Nuclear Science Symposium, Orlando, Florida, October 31 - November 2, 1984.

<sup>•</sup> Work supported in part by the National Science Foundation, grant PHY8115541 and by the Department of Energy, contract DE-AC03-76SF00515.

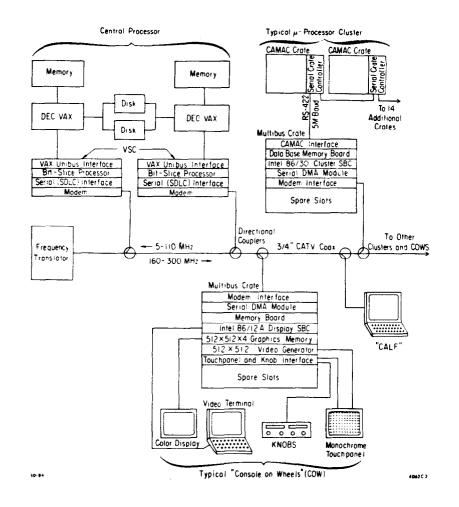

# Fig. 2. The SLC computer control system.

algorithms in order to maximize the SLC performance.

÷

The "old" linac computer control system<sup>2</sup> is based primarily on a "look-and-adjust" manual control system. The SLC requirements preclude this type of control philosophy. Rather, a control philosophy based on machine modeling such as successfully employed in the SPEAR<sup>3</sup> and PEP<sup>4</sup> storage rings is required. Further, the old system has its roots based on technology that is nearly twenty years old. Therefore, the linac l&C is being replaced by a new system that will assume the functions of the present system plus provide a greatly enhanced capability for the precision control and monitoring of devices as well as the implementation of a model driven control system.

The complexity of the SLC project has dictated the "new" control system be implemented in several phases such that it can be installed and made operational without disturbing the continuing operation of accelerator components and so that it can be used to support the development efforts of accelerator physicists who are testing and studying the various accelerator systems as they become available for SLC use. To this end, the first phase of the control system became operational in 1981 to support the testing of the injector and the first linac sector. This system was based on the use of a mixture of SLC prototype hardware and older hardware designs from the PEP storage ring control system.<sup>5</sup> In the fall of 1983, the second phase of the system became operational using production quality hardware and software to control most of the equipment in the first third of the linac, the injector, and one damping ring and compressor. This system, which contains nearly all of the control system

components that will be required for the full implementation of the overall control system, has been operational for about a year now. It has been extensively used and a great deal of experience has been obtained with respect to its operation and performance.

Fig. 2. The SLC computer control system.

Further control system efforts will center on the improvement and refinement of the system hardware and software as well as extending the system to serve all SLC accelerator components. In addition, a tremendous amount of applications oriented software must be developed to provide efficient SLC operation. The whole system must be operational for support of the formal SLC start-up activity scheduled to begin in October, 1986.

## 2. The Computer System

In its final state, the SLC computer control system will be an order of magnitude larger and more complex than any of SLAC's other accelerator control systems. The final system provides a combination of two large central processors networked to 70-100  $\mu$ -processor clusters, as shown in the block diagram in Fig. 2. Each of these clusters has the capability of supporting an arbitrary number of 16-bit single-board computers operating in parallel. It is estimated that the initial total processing power placed into operation for the new linac control system alone will be 15-25 times greater than the processing power in the existing system. Further, the system can be easily expanded to include much more processing power in the future.

The  $\mu$ -processor clusters interface directly to the equipment

to be monitored and controlled and are distributed near their related accelerator components. Clusters are located in each of the 30 linac sectors and near the damping rings, electron gun, positron source, etc.

Operator control and monitoring of the system is performed through the use of "Console-On-Wheels" (COW's). Further, access to the system by technical support personnel is provided by the use of portable terminal based "CALF's" which can be easily moved to any geographical location.

The current operational system contains 2 Digital Equipment Corp. (DEC) VAX 11/780's, approximately 50  $\mu$ -processor clusters, 7 COW's, and approximately 40 terminals which can be used as CALF's.

# 2.1 HARDWARE ARCHITECTURE

2.1.1 Central Computers: The heart of the SLC computer system is based on two DEC VAX systems each with twin disks. These computers provide on-line execution of large modeling programs and serve to interface with the machine operators in order to direct the overall efforts of the control system. These computers also serve as a base for both the VAX and  $\mu$ -processor software development efforts.

The system is currently operated with one VAX serving as the "on-line" processor while the second one serves to support the development effort. In the event of a hardware failure, the roles of the computers can be interchanged with relatively simple hardware switching operations.

The VAX's have been chosen for use as central computers because their virtual-memory operating system can simultaneously support many physically large, CPU-bound operating programs and on-line users, as well as provide an environment for fast, efficient program development and maintenance. There are other processors which can also provide these features, but the VAX was chosen because of extensive hardware and software support already existing at SLAC.

2.1.2 <u>Micro-Processor Clusters:</u> The distributed  $\mu$ -processor clusters are based on the Intel Multibus architecture. This architecture provides support for the arbitrary number of single-board computers (SBC) which communicate with each other through the use of shared memory and interrupts. Currently, the  $\mu$ -processor clusters contain an Intel 86/30 SBC, 768 kilobytes of RAM and 8 kilobytes of EPROM. Various benchmark tests have shown that each  $\mu$ -processor cluster has somewhere between 1/10 and 1/7 the processing power of the VAX 11/780.

The actual interfaces to the SLC technical components will be made through the use of CAMAC. The CAMAC crates are located very near to their related equipment. It is anticipated that the entire SLC system will eventually contain ~250 crates. The crates are interfaced to their respective Multibus crates through high-speed (10  $\mu$ sec/cycle) low-cost serial crate controllers that were developed at SLAC. The Multibus/CAMAC interface is a high-speed Direct Memory Address (DMA) device that directly executes lists of CAMAC commands from the Multibus addess space.

The choice of specific equipment for the  $\mu$ -processor cluster was carefully examined with respect to the FASTBUS architecture. The powerful and flexible FASTBUS architecture easily meets all of the cluster requirements and could potentially be used to replace both the Multibus and CAMAC crates. However, the overall SLC schedule did not allow adequate time to develop and support a FASTBUS implementation of the  $\mu$ processor clusters. In contrast, both Multibus and CAMAC are mature systems that are well supported by industry and within SLAC.

2.1.3 Communications Network: Almost all SLC communications are based on the use of a broadband (5-300 MHz) Cable Television (CATV) system<sup>6</sup> that has the capability to support several hundred frequency-divided communications channels on a single 3/4 inch coaxial cable. This cable is installed in all equipment areas, control rooms, and laboratory development areas. Approximately 5 miles of cable has been installed to date and it is anticipated that the system will eventually extend over 7 miles.

A high-speed one Megabaud polled network<sup>7</sup> has been developed at SLAC to interconnect the  $\mu$ -processor clusters with the VAX's. This network is based on an SDLC<sup>5</sup> protocol and uses a bit-sliced  $\mu$ -processor to direct the sequential polling operation and to serve as a high-speed DMA channel into the VAX. The  $\mu$ -processor clusters communicate with the network by using commercially available SDLC communications modules and modems. The use of a bit-sliced  $\mu$ -processor as the network controller allows the system to poll at a rate in excess of 1200 polls/second.

Terminal to VAX communications are supported with commercially available equipment using protocols similar to Ethernet. Several hundred terminals are supported on one 125 kHz cable channel.

The cable also provides several television, voice and pointto-point data channels.

2.1.4 Operator Consoles: The system contains two types of operator consoles. A more elaborate type has been given the name of Console-On-Wheels (COW) because it is a fully portable unit which may be connected to any of the CATV communications system ports. It contains a 4 color, 512 element x 512 line graphics display; a 8x8 button touch panel; 8 general purpose slew knobs; and an Ann Arbor Ambassador VDT. The COW is based on the Multibus architecture and contains a SBC to provide local intelligence.

The second type of console is called a CALF because it is a smaller (more portable) and less expensive version of the COW. It consists of an Ann Arbor Ambassador terminal and modem which allows it to be attached to the CATV system. The CALF can emulate a subset of the COW functions and nearly any operation that can be performed using a COW can also be performed using the CALF without the development of special software.

Although the CALF was developed to be primarily used by technical support personnel for maintenance and development activities, it has found wide use for direct control of the accelerator in applications where the high cost of the COW cannot be justified.

#### 2.2 COMPUTER SYSTEM SOFTWARE ARCHITECTURE

Essentially all of the SLC software development is performed through the use of the VAX. Wherever possible, FORTRAN 77 is used for applications programming in both the VAX and the  $\mu$ -processor clusters. FORTRAN 77 was chosen as the standard language because of its extensive support in the VAX, and because it is the most universally understood language. Although alternative languages could be used for the  $\mu$ -processors, the consistency provided by standardizing on FORTRAN 77 has

| Module Name<br>(acronym)                       | Source                                            | Approximate No.<br>of modules to<br>be used in the<br>system | . Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Use                                                                                                                                                                        |

|------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial<br>Crate<br>Controller<br>(SCC)         | SLAC .                                            | <b>2</b> 50                                                  | Serves as a CAMAC Crate Controller. In-<br>terfaces to a host computer via 2 RS-422<br>level signals on a twisted pair cable. An<br>entire cycle, consisting of receiving a com-<br>mand, executing the CAMAC cycle, and<br>responding, is performed in ~10 $\mu$ seconds.<br>The bit data rate is 5 MHz. 16 controllers<br>may be run from a single daisy-chained<br>cable at distances in excess of 2000 feet<br>with repeaters. (double-width).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Used as the Standard SLC Crate Con-<br>troller.                                                                                                                            |

| Crate Verifier                                 | SLAC                                              | <b>2</b> 50                                                  | Contains command line spy register, inde-<br>pendent function read and write register,<br>LAM testing registers, and supply volt-<br>age and local temperature measurement<br>capability. (single-width).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Used to verify proper crate and crate<br>controller operation and aid in prob-<br>lem diagnosis.                                                                           |

| Smart<br>Analog<br>Monitor<br>(SAM)            | Transiac Co<br>or Standard<br>Engineering<br>Inc. | -                                                            | Provides 32 differential channels of $\mu$ -processor controlled digitization. Rang-<br>ing, polarity selection, and self calibration<br>are fully automatic. The module may be<br>operated in the "slow" mode where each<br>channel is integrated for one 60 Hz period<br>(16.67 ms) or in a fast mode where each<br>channel is digitized in 2 milliseconds. AC<br>voltage is also read for each channel. All<br>data is stored in a local memory and can<br>be read asynchronously with the digitiz-<br>ing process. Accommodates full-scale in-<br>puts from 10 mV to 10.24 V and digitizes<br>the signal with a resolution of 14 bits. The<br>digitized value is presented in either VAX<br>or IEEE floating print formats. The mod-<br>ule may be interfaced to thermocouples by<br>dedicating one of its input channels to a<br>reference temperature thermister. In this<br>mode the module can be programmed to<br>provide the thermocouple junction tem-<br>perature directly. (single-width). | Temperature monitoring of Linac<br>waveguide. Monitoring of multi-<br>channel "small" analog power sup-<br>plies. Monitoring of miscellaneous<br>analog reference signals. |

| Transiac<br>DAC<br>(DAC)                       | Transiac Co                                       | гр. <b>275</b>                                               | Provide 16 channels of analog output with<br>a full scale range of $\pm 10V$ , a resolution<br>of 16 bits, and a basic accuracy of .01%.<br>(single-width).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Used to control multi-channel "small"<br>power supplies and miscellaneous de-<br>vices such as illumination for beam<br>profile monitors.                                  |

| Isolated Digital<br>Input Module<br>(IDIM)     | SLAC                                              | 200                                                          | Contains 32 optically isolated non-latching<br>digital input channels. (single-width).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Used for reading miscellaneous digi-<br>tal status information.                                                                                                            |

| Isolated<br>Digital<br>Output Module<br>(IDOM) | SLAC                                              | 100                                                          | Contains 32 channels of open-collector op-<br>tically isolated digital output. Each chan-<br>nel may be programmed to latch its out-<br>put data or to pulse high or low for a pre-<br>scribed time period. (single-width).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Used for controlling digital devices<br>such as beam screens, power supply<br>on/off controls, etc.                                                                        |

\* \*\*

i.

| Pulsed Power<br>Output Module<br>(PPOM)          | SLAC | 75  | Provides a minus 24 volt output pulse with<br>a nominal duration of 1/4 second to any<br>one of 32 channels. (single-width).                                                                                                                                                                                                                      | Primarily used to replace the "Re-<br>mote Control System" in the Linac.                                                         |

|--------------------------------------------------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Power Supply<br>Controller<br>(PSC)              | SLAC | 175 | • • •                                                                                                                                                                                                                                                                                                                                             | Primarily used to control and mon-<br>itor "large" power supplies.                                                               |

| Programmable<br>Delay<br>Unit<br>(PDU)           | SLAC | 175 | Contains 16 channels of programmable<br>pulse delay. Delay resolution is 8.4 ns and<br>the delay is adjustable to 2.7 ms. The<br>module is driven at its front panel by 476<br>MHz square wave with a missing pulse<br>serving as the "start delay" fiducial. All<br>outputs are provided to the CAMAC aux-<br>illiary backplane. (double-width). | Used to time modules and devices<br>such as BPMs, PAUs, PIOPs, etc.,<br>which must be synchronised to the<br>beam (see Ref. 9).  |

| Single<br>Timing<br>Buffer<br>(STB)              | SLAC | 175 | Contains buffers to supply the 16 PDU<br>channels to external destinations. Also<br>contains a high-speed timer to measure<br>delay of any channel for diagnostic pur-<br>poses (single-width).                                                                                                                                                   | Used in conjunction with a PDU to<br>verify its correct operation and to<br>buffer its pulses.                                   |

| Programmable<br>Synchronization<br>Unit<br>(PSU) | SLAC | 5   | Provides a chain of "N" NIM level pulses<br>of width W at pulse period of P after a<br>delay D, where N, W, P and D are pro-<br>grammable in the module. The module is<br>driven at its front panel by a 476 MHs<br>square wave with a missing pulse serv-<br>ing as the "start delay" fiducial. (double-<br>width).                              | Used to synchronize devices to the damping ring beam.                                                                            |

| Programmable<br>Width Unit<br>(PWU)              | SLAC | 10  | Receives 8 delayed triggers from the CA-<br>MAC upper backplane and provides out-<br>put pulses with a programmed duration.<br>(double-width).                                                                                                                                                                                                    | Used in applications where programmed<br>duration synchronisation or gated pulses<br>are required, such as gun triggers,<br>etc. |

| Vernier<br>Delay<br>Unit<br>(VDU)                | SLAC | 5   | Provides 2 channels of Vernier delay for<br>timing signals selected from the auxiliary<br>backplane or from front panel connectors.<br>The delay resolution is 1 nanosecond and<br>the range is 10.5 nanoseconds (single-width)                                                                                                                   | Used in applications when the 8.2<br>nanosecond resolution to the PDU<br>is not sufficient                                       |

| Cable<br>Access<br>Transmitter<br>CAT)           | SLAC | 5   | Transmits a 2 Megabaud SDLC bit stream<br>on the CATV cable. 16 bit parallel data<br>may be supplied from the CAMAC back-<br>plane or from a front panel connector. Used<br>in conjunction with one or more Cable<br>Access Receivers (CARs). Can be set to<br>transmit on any of 5 CATV channels (triple-<br>width).                             | See CAR usage below.                                                                                                             |

| Transmitter                                      |      |     | may be supplied from the CAMAC back-<br>plane or from a front panel connector. Used<br>in conjunction with one or more Cable<br>Access Receivers (CARs). Can be set to<br>transmit on any of 5 CATV channels (triple-                                                                                                                             |                                                                                                                                  |

- 5 -

| Cable<br>Access<br>Receiver<br>(CAR)         | SLAC                       | 100         | bit stream from the CATV cable and con-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Used in specialised point-to-point dig-<br>ital communications applications. One<br>main use is in the Beam Pattern Sys-<br>tem where one CAT, driven by a<br>$\mu$ -processor transmits beam related<br>information at the accelerator cycle<br>rate (360 Hs) to approximately 100<br>CARs which receive the information<br>simultaneously and forward it to their<br>related $\mu$ -processors. Also used in<br>digital beam feedback loops. |

|----------------------------------------------|----------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Video<br>Cable<br>Access<br>Module<br>(VCAM) | Coherent Sys-<br>tems Inc. | 25          | Can be programmed to accept one of eight<br>video (TV camera) inputs and place it on<br>one of five possible CATV channels. The<br>images may then be observed anywhere in<br>the system using standard television re-<br>ceivers. (double-width).                                                                                                                                                                                                                                                                                                                  | Used to multiplex TV camera sig-<br>nals to operator control stations.                                                                                                                                                                                                                                                                                                                                                                         |

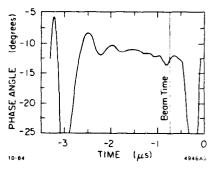

| Parallel<br>I/O<br>Processor<br>(PIOP)       | SLAC                       | <b>2</b> 50 | Contains an Intel 8088 processor which<br>supports both RAM and EPROM mem-<br>ory. Has a general purpose interface to the<br>CAMAC backplane and contains a front<br>panel I/O port that supports a differential<br>driver/receiver version of the 8088 I/O bus.<br>It is designed to be used with special pur-<br>pose "heads" which provide an interface<br>to a device. Its program may reside in<br>EPROM or may be downloaded from a<br>VAX. Cross-compilers and network sup-<br>ported software exist to aid in the devel-<br>opment process. (single-width). | Primary use to date has centered on<br>the klystron control for the Linac. <sup>10</sup><br>Phase & Amplitude Detector (PAD) <sup>11</sup><br>and Modulator Klystrons Control (MKII<br>heads have been developed to allow<br>PIOP to monitor and control a klystron,<br>its modulator and to measure its out-<br>put phase and amplitude with re-<br>spect to a stable reference. See Fig-<br>ure 3.                                           |

| Beam Position<br>Monitor<br>BPM)             | SLAC                       | 325         | Provides 12 bits of resolution and 8 bits<br>of attenuation control as well as a self-<br>calibration mode to digitize fast (1 ns)<br>bipolar pulses. (double-width).                                                                                                                                                                                                                                                                                                                                                                                               | Digitizes signals derived from beam position monitor striplines.                                                                                                                                                                                                                                                                                                                                                                               |

| Beam Position<br>Multiplexer<br>(SP10T)      | SLAC                       | 325         | Provides a single pole 10 throw (SP10T)<br>switch for fast (1 ns) bipolar signals. (single-<br>width).                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Used to multiplex beam position mon-<br>itor signals into the BPM modules in<br>some applications.                                                                                                                                                                                                                                                                                                                                             |

| Pulsed<br>Amplitude<br>Unit<br>(PAU)         | SLAC                       | 25          | Provides 32 "time-multiplexed" channels<br>of pre- programmed analog amplitude. Re-<br>ceives timing information from CAMAC<br>auxiliary backplanes and pattern informa-<br>tion from the CAMAC backplane. (single-<br>width).                                                                                                                                                                                                                                                                                                                                      | Used for the control of devices such<br>as pulsed magnets and phase shifters<br>which must change state at the ac-<br>celerator pulse rate (360 MHz).                                                                                                                                                                                                                                                                                          |

| Toroid Charge<br>Monitor (TCM)               | SLAC                       | 15          | Digitizes a signal generated by charge pass-<br>ing through a toroid with a nominal 1%<br>accuracy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Used to digitize beam current inten-<br>sities.                                                                                                                                                                                                                                                                                                                                                                                                |

. .

been a great advantage for both the development and support of applications programs.

A significant effort has been expended by SLAC to create an efficient and user-friendly environment for the development of  $\mu$ -processor software. In collaboration with the Intel Corp., FORTRAN 77 and PLM 86 cross-compilers, a cross-assembler, and a cross-linker have been developed to support the 8086/8088 series of  $\mu$ -processors. Further, a symbolic debugger has been developed to allow the remote debugging of  $\mu$ -processor based programs.

Applications tasks executed in the VAX are written as structured subroutines which are attached to a VAX process that provides interface routines to the operator console, and to a structured database. This process also provides a scheduling service for the subroutines.

The  $\mu$ -processor clusters provide local control algorithms for the operation of the technical equipment. In general, the  $\mu$ -processors receive an operational configuration in engineering units for their equipment from the VAX. They then ensure that the equipment is set to that configuration and only report back to the VAX when they are unable to achieve or maintain the desired configuration. The  $\mu$ -processor clusters also provide monitoring information in engineering units to the VAX upon request and support a "pass-thru" mode for I/O commands from the VAX. The I/O commands may originate from a VAX applications process or from a system user via individual or a file of interpretive commands. The  $\mu$ -processor systems will be used in the future to implement time-sensitive digital control loops.

### 3. Equipment Interfaces

In its completed state, the SLC control system will contain more than 250 CAMAC crates housing over 3200 CAMAC modules that provide I/O capability for nearly 50,000 signal points. Because of the size of these requirements, a significant development effort has been made to develop a comprehensive and flexible complement of CAMAC modules that serve to interface the SLC technical equipment to the computer system. Table 1 provides a listing and description of the interface modules used in the SLC system as well as typical applications.

### 4. Operational Experience

Although a portion of the control system has now been fully operational for a year, the project is still in its infancy and, as anyone who has been involved with a large system at this point in its evolution can appreciate, most of our current thoughts regarding the performance of the system relate to those items that must be improved. We are committed to the defining and implementing of improvement programs and have simply overlooked or forgotten to identify the many real successes of the system. With this thought in mind, we present the following list of observations regarding the performance of the system to date and generalize the successes of the system by stating that over the past year it has successfully supported the needs of accelerator physicists and machine operators in a series of very important and demanding operating experiments that have proven the viability of the SLC project.

- It is extremely important to be able to trace problems efficiently in the system's operating environment. Although

- an extensive effort has been applied to providing remote debugging tools and comprehensive diagnostics, significant

resources will continue to be directed to support these efforts.

- The number of simultaneous users of the system has been overwhelming at times. It is not unusual to have 5 COW's, 5-7 CALFS, and 2-3 program development terminals simultaneously active on a single VAX. Though current response-times for the system may be tolerable even under heavily loaded conditions with our current configuration, it is evident that we will have to do battle with a response-time problem as the system expands to its fullyimplemented state.

- It is evident that the "information bandwidth" to the operator provided by a single COW as currently configured is not sufficient for efficient performance. This problem will probably have to be attacked by providing more devices (touchpanels, CRT's etc.) as well as increasing the performance of those devices.

- The system has been designed to support a diversity of operating and support personnel and it has been very successful in that regard, However, this success has developed into a tremendous need for user oriented software such that our relatively small software staff is greatly overloaded. In addition to continuing on a best efforts basis to provide this software, it is clear that more features and support are required to allow "casual" users programming access to the system so that they can write their own dedicated applications programs and have them supported in an integrated fashion.

Fig. 3. A fast-time plot of the RF phase of a linac klystron pulse relative to a reference line and with respect to time. This plot was made using data supplied by a PIOP module (See Table 1) that collected the 64 data points on consecutive klystron pulses by adjusting a timing trigger delay to the phase detection digitizer on a pulse-to-pulse basis.

### Acknowledgments

Over 100 people at SLAC have been involved with development and implementation of the SLC control system hardware and software, so individual acknowledgments are impossible. But I would like to take this opportunity to collectively thank all the people involved for their dedicated efforts in bringing the system to its current state and wish them the best of luck in their efforts to expand and improve it.

## REFERENCES

- 1. SLAC Linear Collider Conceptual Design Report, Stanford Linear Accelerator Center, SLAC-229 (1980).

- V. Davidson and R. Johnson, "Present SLAC Accelerator Computer Control System Features," IEEE Trans. Nucl. Sci., NS-28 (1981).

- 3. A. M. Boyarski, A. S. King, M. J. Lee, J. R. Rees, and N. Spencer, "Automatic Control Program for SPEAR," IEEE Trans. Nucl. Sci., NS-20, 580-583, (1973).

- 4. A. Chao et al., "PEP Computer Control System," IEEE Trans. Nucl. Sci., NS-26, 3268-3271 (1979).

- 5. R. Melen, "The PEP Instrumentation and Control System," Proceedings of the 11th International Conference on High Energy Accelerators, pp. 408-420 (1980).

- 6. W. Struven, "Wide-Band Cable System at SLAC," IEEE Trans. Nucl. Sci., NS-30 (1983).

- J. D. Fox, E. Linstadt, and R. Melen, "Applications of Local Area Networks to Accelerator Control Systems at the Stanford Linear Accelerator Center," IEEE Trans. Nucl. Sci., NS-30 (1983).

- J. R. Kersey, "Synchronous Data Link Control," Data Communications, McGraw-Hill Publications, 49-60 (May/June 1974).

- 9. E. Linstadt, "The Design of a Semi-Custom Integrated Circuit for the SLAC SLC Timing Control System," paper to be presented at this conference (1984).

- R. Keith Jobe, "A New Control System for the SLAC Accelerator Klystrons for SLC," IEEE Trans. Nucl. Sci., NS-30 (1983).

- J. D. Fox and H. D. Schwarz, "Phase and Amplitude Detector System for the Stanford Linear Accelerator Center," IEEE Trans. Nucl. Sci., NS-30 (1983).