# MVME5500 Single-Board Computer

# Programmer's Reference Guide

V5500A/PG2

October 2003 Edition

## © Copyright 2003 Motorola Inc.

## All rights reserved.

## Printed in the United States of America.

Motorola and the stylized M logo are trademarks of Motorola, Inc., registered in the U.S. Patent and Trademark Office.

All other product or service names mentioned in this document are the property of their respective owners.

## **Safety Summary**

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result in personal injury or damage to the equipment.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the equipment is supplied with a three-conductor AC power cable, the power cable must be plugged into an approved three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes.

#### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in any explosive atmosphere such as in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage.

#### Keep Away From Live Circuits Inside the Equipment.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified service personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Service personnel should not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, such personnel should always disconnect power and discharge circuits before touching components.

#### Use Caution When Exposing or Handling a CRT.

Breakage of a Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, do not handle the CRT and avoid rough handling or jarring of the equipment. Handling of a CRT should be done only by qualified service personnel using approved safety mask and gloves.

## Do Not Substitute Parts or Modify Equipment.

Do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that all safety features are maintained.

## **Observe Warnings in Manual.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

To prevent serious injury or death from dangerous voltages, use extreme caution when handling, testing, and adjusting this equipment and its components.

## **Flammability**

All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating of 94V-0 by UL-recognized manufacturers.

## **EMI Caution**

This equipment generates, uses and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used with adequate EMI protection.

## **Lithium Battery Caution**

This product contains a lithium battery to power the clock and calendar circuitry.

Danger of explosion if battery is replaced incorrectly. Replace battery only with the same or equivalent type recommended by the equipment manufacturer. Dispose of used batteries according to the manufacturer's instructions.

Il y a danger d'explosion s'il y a remplacement incorrect de la batterie. Remplacer uniquement avec une batterie du même type ou d'un type équivalent recommandé par le constructeur. Mettre au rebut les batteries usagées conformément aux instructions du fabricant.

Explosionsgefahr bei unsachgemäßem Austausch der Batterie. Ersatz nur durch denselben oder einen vom Hersteller empfohlenen Typ. Entsorgung gebrauchter Batterien nach Angaben des Herstellers.

## **CE Notice (European Community)**

This is a Class A product. In a domestic environment, this product may cause radio interference, in which case the user may be required to take adequate measures.

Motorola Computer Group products with the CE marking comply with the EMC Directive (89/336/EEC). Compliance with this directive implies conformity to the following European Norms:

EN55022 "Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment"; this product tested to Equipment Class A

EN55024 "Information technology equipment—Immunity characteristics—Limits and methods of measurement"

Board products are tested in a representative system to show compliance with the above mentioned requirements. A proper installation in a CE-marked system will maintain the required EMC performance.

In accordance with European Community directives, a "Declaration of Conformity" has been made and is available on request. Please contact your sales representative.

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to the Motorola Computer Group Web site. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Motorola, Inc.

It is possible that this publication may contain reference to or information about Motorola products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

## **Limited and Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

## **Contents**

| About This Guide                                               |      |

|----------------------------------------------------------------|------|

| Summary of Changes                                             | xiii |

| Overview of Contents                                           | xiii |

| Comments and Suggestions                                       | xiv  |

| Conventions Used in This Manual                                | xiv  |

|                                                                |      |

| CHAPTER 1 Board Description and Memory Maps                    |      |

| Introduction                                                   | 1-1  |

| Overview                                                       | 1-1  |

| Memory Maps                                                    | 1-5  |

| Default Processor Memory Map                                   |      |

| MOTLoad's Processor Memory Map                                 |      |

| Default PCI Memory Map                                         |      |

| MOTLoad's PCI Memory Maps                                      | 1-9  |

| PCI I/O Space Maps                                             | 1-9  |

| System I/O Memory Map                                          | 1-10 |

| System Status Register 1                                       | 1-11 |

| System Status Register 2                                       | 1-13 |

| System Status Register 3                                       |      |

| Presence Detect Register                                       |      |

| Configuration Header/Switch Register (S1)                      |      |

| Time Base Enable Register                                      |      |

| Geographical Address Register (S2)                             |      |

| COM1 & COM2 Universal Asynchronous Receiver/Transmitter (UART) |      |

| Real-Time Clock and NVRAM                                      |      |

| ISA Local Resource Bus                                         | 1-20 |

| CHAPTER 2 Programming Details                                  |      |

| Introduction                                                   | 2.1  |

|                                                                |      |

| PCI Configuration Space and IDSEL Mapping                      |      |

| Interrupt Controller                                           |      |

| Two-Wire Serial Interface                                      |      |

| GT-64260B Initialization                                       |      |

| GT-64260B GPP Configuration                                    | 2-7  |

| GT-64260B Reset Configuration                | 2-9  |

|----------------------------------------------|------|

| GT-64260B Device Controller Bank Assignments | 2-11 |

| System Clock Generators                      | 2-13 |

| VPD and User Configuration EEPROMs           | 2-14 |

| Temperature Sensor                           | 2-14 |

| Flash Memory                                 | 2-14 |

| PCI Arbitration Assignments                  | 2-14 |

| Other Software Considerations                |      |

| CPU Bus Mode                                 | 2-15 |

| Processor Type Identification                | 2-16 |

| Processor PLL Configuration                  | 2-16 |

| L1, L2, L3 Cache                             | 2-16 |

| APPENDIX A Vital Product Data                |      |

| Flash Memory Configuration Data              | A-1  |

| L3 Cache Configuration Data                  |      |

| APPENDIX B Related Documentation             |      |

| Motorola Computer Group Documents            | B-1  |

| Manufacturers' Documents                     | B-2  |

| Related Specifications                       | B-5  |

|                                              |      |

## **List of Figures**

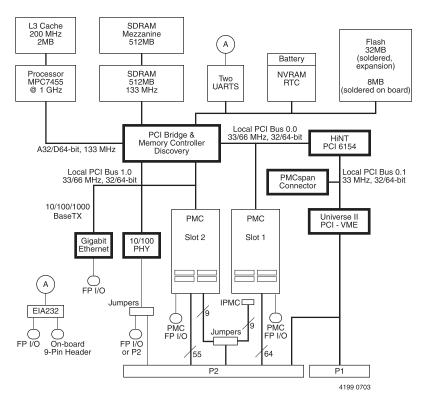

| Figure | 1-1. | . MVME5500 | <b>Block Diagram</b> | <br>-4 |

|--------|------|------------|----------------------|--------|

|        |      |            |                      |        |

## **List of Tables**

| Table 1-1. MVME5500 Features Summary                    | 1-2  |

|---------------------------------------------------------|------|

| Table 1-2. Default Processor Memory Map                 | 1-5  |

| Table 1-3. MOTLoad's Processor Memory Map               | 1-6  |

| Table 1-4. Default PCI Memory Map                       | 1-7  |

| Table 1-5. MOTLoad's PCI 0 Domain Memory Map            | 1-9  |

| Table 1-6. MOTLoad's PCI 1 Domain Memory Map            | 1-9  |

| Table 1-7. PCI 0 Domain I/O Map                         | 1-9  |

| Table 1-8. PCI 1 Domain I/O Map                         |      |

| Table 1-9. Device Bank 1 I/O Memory Map                 | 1-10 |

| Table 1-10. System Status Register 1                    | 1-11 |

| Table 1-11. System Status Register 2                    | 1-13 |

| Table 1-12. System Status Register 3                    | 1-15 |

| Table 1-13. Presence Detect Register                    | 1-16 |

| Table 1-14. Configuration Header/Switch Register        |      |

| Table 1-15. TBEN Register                               | 1-18 |

| Table 1-16. Geographical Address Register               | 1-19 |

| Table 2-1. IDSEL Mapping for PCI Devices                | 2-2  |

| Table 2-2. GT-64260B External GPP Interrupt Assignments | 2-4  |

| Table 2-3. I2C Bus Device Addressing                    | 2-6  |

| Table 2-4. GT-64260B GPP Pin Function Assignments       | 2-7  |

| Table 2-5. GT-64260B Power-Up Configuration Settings    |      |

| Table 2-6. Device Bank Assignments                      | 2-12 |

| Table 2-7. Device Bank Timing Parameters                |      |

| Table 2-8. PCI Arbiter Assignments                      | 2-15 |

| Table 2-9. Processor L3CR Register Assignments          | 2-16 |

| Table A-1. Flash 0 Memory Configuration Data            | A-1  |

| Table A-2. Flash 1 Memory Configuration Data            | A-2  |

| Table A-3. L3 Cache Configuration Data                  | A-3  |

| Table B-1. Motorola Computer Group Documents            | B-1  |

| Table B-2. Manufacturers' Documents                     | B-2  |

| Table B-3. Related Specifications                       | B-5  |

## **About This Guide**

The MVME5500 Single-Board Computer Programmer's Reference Guide provides general programming information, including memory maps, interrupts, and register data for the MVME5500 family of boards. This document should be used by anyone who wants general, as well as technical information about the MVME5500 products.

As of the printing date of this manual, the MVME5500 supports the models listed below.

| Model Number  | Description                                             |  |  |

|---------------|---------------------------------------------------------|--|--|

| MVME5500-0161 | 1 GHz MPC7455 processor, 512MB SDRAM,<br>Scanbe handles |  |  |

| MVME5500-0163 | 1 GHz MPC7455 processor, 512MB SDRAM, IEEE handles      |  |  |

## **Summary of Changes**

This is the second edition of the *Programmer's Reference Manual*. It supersedes the August 2003 edition and incorporates the following changes.

| Date            | Changes                                                                       |  |

|-----------------|-------------------------------------------------------------------------------|--|

| October<br>2003 | Corrected the PCI 0 and 1 domain memory space sizes in Table 1-3 on page 1-6. |  |

## **Overview of Contents**

This manual is divided into the following chapters and appendices:

Chapter 1, *Board Description and Memory Maps*, provides a brief product description and a block diagram. The remainder of the chapter provides information on memory maps and system and configuration registers.

Chapter 2, *Programming Details*, provides additional programming information including IDSEL mapping, interrupt assignments for the GT-64260B system processor, two-wire serial interface addressing, and other device and system considerations.

Appendix A, *Vital Product Data*, provides a listing of vital product data (VPD) related to this product.

Appendix B, *Related Documentation*, provides a listing of related Motorola manuals, vendor documentation, and industry specifications.

## **Comments and Suggestions**

Motorola welcomes and appreciates your comments on its documentation. We want to know what you think about our manuals and how we can make them better. Mail comments to:

Motorola Computer Group Reader Comments DW164 2900 S. Diablo Way Tempe, Arizona 85282

You can also submit comments to the following e-mail address: reader-comments@mcg.mot.com

In all your correspondence, please list your name, position, and company. Be sure to include the title and part number of the manual and tell how you used it. Then tell us your feelings about its strengths and weaknesses and any recommendations for improvements.

## **Conventions Used in This Manual**

The following typographical conventions are used in this document:

#### bold

is used for user input that you type just as it appears; it is also used for commands, options and arguments to commands, and names of programs, directories and files.

#### italic

is used for names of variables to which you assign values, for function parameters, and for structure names and fields. Italic is also used for comments in screen displays and examples, and to introduce new terms.

#### courier

is used for system output (for example, screen displays, reports), examples, and system prompts.

#### <Enter>, <Return> or <CR>

represents the carriage return or Enter key.

#### Ctrl

represents the Control key. Execute control characters by pressing the Ctrl key and the letter simultaneously, for example, Ctrl-d.

# Board Description and Memory Maps

## Introduction

This chapter briefly describes the board level hardware features of the MVME5500 single-board computer, including a table of features and a block diagram. The remainder of the chapter provides memory map information including a default memory map, MOTLoad's processor memory map, a default PCI memory map, MOTLoad's PCI memory map, a PCI I/O memory map, and system I/O memory maps.

Programmable registers in the GT-64260B system controller are documented in publication MV-S100414-00 Rev A, which is obtainable from Marvell Technologies, Ltd. Refer to Appendix B, *Related Documentation* for more information.

## **Overview**

The MVME5500 is a single-board computer based on the PowerPC MPC7455 processor and the Marvell GT-64260B host bridge with a dual PCI interface and memory controller. On-board payload includes two PMC slots, two SDRAM banks, an expansion connector for two additional banks of SDRAM, 8MB boot Flash ROM, one 10/100/1000 Ethernet port, one 10/100 Ethernet port, 32MB expansion Flash ROM, two serial ports, and an NVRAM and real-time clock.

The following table lists the features of the MVME5500.

Table 1-1. MVME5500 Features Summary

| Feature               | Description                                                                                                                                                                                                                                                                            |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Processor             | <ul><li>Single 1 GHz MPC7455 processor</li><li>Bus clock frequency at 133 MHz</li></ul>                                                                                                                                                                                                |  |  |

| L3 Cache              | - 2MB using DDR SRAM - Bus clock frequency at 200 MHz                                                                                                                                                                                                                                  |  |  |

| Flash                 | <ul> <li>8MB Flash soldered on board</li> <li>32MB expansion Flash soldered on board</li> </ul>                                                                                                                                                                                        |  |  |

| System Memory         | <ul> <li>Two banks on-board for 512MB using 256Mb devices</li> <li>Expansion connector for a mezzanine board with two banks for 512MB using 256Mb devices</li> <li>Double-bit-error detect, single-bit-error correct across 72 bits</li> <li>Bus clock frequency at 133 MHz</li> </ul> |  |  |

| Memory Controller     | <ul> <li>Provided by GT-64260B</li> <li>Supports one to four banks of SDRAM at up to 1GB per bank</li> </ul>                                                                                                                                                                           |  |  |

| Processor Host Bridge | <ul><li>– Provided by GT-64260B</li><li>– Supports MPX mode or 60x mode</li></ul>                                                                                                                                                                                                      |  |  |

| PCI Interfaces        | <ul> <li>Provided by GT-64260B</li> <li>Two independent 64-bit interfaces, one compliant to PCI spec rev</li> <li>2.1 (Bus 0.0) and the other compliant to PCI spec rev 2.2 (Bus 1.0)</li> <li>Bus clock frequency at 66 MHz</li> </ul>                                                |  |  |

|                       | <ul> <li>Provided by the HiNT PCI 6154 secondary interface</li> <li>One 64-bit interface, compliant to PCI spec rev 2.1 (Bus 0.1)</li> <li>Bus clock frequency at 33 MHz</li> </ul>                                                                                                    |  |  |

| Interrupt Controller  | <ul> <li>Provided by GT-64260B</li> <li>Interrupt sources internal to GT-64260B</li> <li>Up to 32 external interrupt inputs</li> <li>Up to seven interrupt outputs</li> </ul>                                                                                                          |  |  |

| Counters/Timers       | - Eight 32-bit counters/timers in GT-64260B                                                                                                                                                                                                                                            |  |  |

Table 1-1. MVME5500 Features Summary (continued)

| Feature                        | Description                                                                                                                                                     |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| I2C                            | <ul> <li>Provided by GT-64260B</li> <li>Master or slave capable</li> <li>On-board serial EEPROMs for VPD, SPD, GT-64260B init, and user data storage</li> </ul> |  |

| NVRAM                          | - 32KB provided by MK48T37                                                                                                                                      |  |

| Real Time Clock                | - Provided by MK48T37                                                                                                                                           |  |

| Watchdog Timers                | <ul> <li>One in GT-64260B</li> <li>One in MK48T37</li> <li>Each watchdog timer can generate interrupt or reset, software selectable</li> </ul>                  |  |

| On-board Peripheral<br>Support | <ul> <li>One 10/100/1000BaseT Ethernet interface, one 10/100BaseT</li> <li>Ethernet interface</li> <li>Dual 16C550 compatible UARTs</li> </ul>                  |  |

| PCI Mezzanine Cards            | - Two PMC sites (one shared with the expansion memory and has IPMC capability)                                                                                  |  |

| PCI Expansion                  | - One expansion connector for interface to PMCspan                                                                                                              |  |

| Miscellaneous                  | <ul><li>Reset/Abort switch</li><li>Front panel status indicators, Run and Board Fail</li></ul>                                                                  |  |

| Form Factor                    | - Standard VME                                                                                                                                                  |  |

Figure 1-1. MVME5500 Block Diagram

## **Memory Maps**

## **Default Processor Memory Map**

When power is first applied or a hard reset has occurred, the GT-64260B has a default address map. Table 1-2 shows the default processor memory map.

**Table 1-2. Default Processor Memory Map**

| Processor Address |           |        |                          |       |

|-------------------|-----------|--------|--------------------------|-------|

| Start             | End       | Size   | Definition               | Notes |

| 0000 0000         | 007F FFFF | 8MB    | SDRAM Bank 0             |       |

| 0080 0000         | 00FF FFFF | 8MB    | SDRAM Bank 1             |       |

| 0100 0000         | 017F FFFF | 8MB    | SDRAM Bank 2             |       |

| 0180 0000         | 01FF FFFF | 8MB    | SDRAM Bank 3             |       |

| 0200 0000         | 0FFF FFFF | 224MB  | Unassigned               |       |

| 1000 0000         | 11FF FFFF | 32MB   | PCI Bus 0 I/O Space      |       |

| 1200 0000         | 13FF FFFF | 32MB   | PCI Bus 0 Memory Space 0 |       |

| 1400 0000         | 1BFF FFFF | 128MB  | Unassigned               |       |

| 1C00 0000         | 1C7F FFFF | 8MB    | Device Port CS0          |       |

| 1C80 0000         | 1CFF FFFF | 8MB    | Device Port CS1          |       |

| 1D00 0000         | 1DFF FFFF | 16MB   | Device Port CS2          |       |

| 1E00 0000         | 1FFF FFFF | 32MB   | Unassigned               |       |

| 2000 0000         | 21FF FFFF | 32MB   | PCI Bus 1 I/O            |       |

| 2200 0000         | 23FF FFFF | 32MB   | PCI Bus 1 Memory Space 0 |       |

| 2400 0000         | 25FF FFFF | 32MB   | PCI Bus 1 Memory Space 1 |       |

| 2600 0000         | 27FF FFFF | 32MB   | PCI Bus 1 Memory Space 2 |       |

| 2800 0000         | 29FF FFFF | 32MB   | PCI Bus 1 Memory Space 3 |       |

| 2A00 0000         | F0FF FFFF | 3184MB | Unassigned               |       |

**Table 1-2. Default Processor Memory Map (continued)**

| Processor Address |           |                |                          |       |

|-------------------|-----------|----------------|--------------------------|-------|

| Start             | End       | Size           | Definition               | Notes |

| F100 0000         | F100 FFFF | 64KB           | Internal Registers       | 1     |

| F101 0000         | F1FF FFFF | 16MB -<br>64KB | Unassigned               |       |

| F200 0000         | F3FF FFFF | 32MB           | PCI Bus 0 Memory Space 1 |       |

| F400 0000         | F5FF FFFF | 32MB           | PCI Bus 0 Memory Space 2 |       |

| F600 0000         | F7FF FFFF | 32MB           | PCI Bus 0 Memory Space 3 |       |

| F800 0000         | FEFF FFFF | 112MB          | Unassigned               |       |

| FF00 0000         | FF7F FFFF | 8MB            | Device Port CS3          |       |

| FF80 0000         | FFFF FFFF | 8MB            | Boot Flash Bank          | 2     |

## **Notes** 1. Set by configuration resistors.

2. Selects Flash 0 or Flash 1 depending on the state of the Flash boot bank select jumper.

## **MOTLoad's Processor Memory Map**

MOTLoad's processor memory map is given in the following table.

Table 1-3. MOTLoad's Processor Memory Map

| Processor Address |           |       |                           |       |

|-------------------|-----------|-------|---------------------------|-------|

| Start             | End       | Size  | Definition                | Notes |

| 0000 0000         | 7FFF FFFF | 2GB   | On-Board SDRAM            | 1     |

| 8000 0000         | DFFF FFFF | 1.5GB | PCI 0 Domain Memory Space |       |

| E000 0000         | EFFF FFFF | 256MB | PCI 1 Domain Memory Space |       |

| F000 0000         | F07F FFFF | 8MB   | PCI 0 Domain I/O Space    | 2     |

| F080 0000         | F0FF FFFF | 8MB   | PCI 1 Domain I/O Space    | 2     |

Processor Address Start End Size **Definition** Notes F100 0000 F10F FFFF GT-64260B Internal Registers 1MB F110 0000 F11F FFFF GT-64260B Device Bus Registers 3 1MB F120 0000 F1FF FFFF 14MB Reserved F200 0000 FE00 0000 32MB Flash Bank 0 4 FFFF FFFF 4 FF80 0000 8MB Flash Bank 1

Table 1-3. MOTLoad's Processor Memory Map (continued)

#### Notes

- 1. Maximum size is 2GB. Actual size depends on the amount of memory installed.

- 2. Zero-based I/O space.

- 3. Device chip select 1.

- 4. Flash 0/Flash 1 can be mapped to device chip select 0 or BOOT chip select depending on the state of the Flash boot bank select header.

## **Default PCI Memory Map**

Table 1-4 is the default PCI memory map for each PCI bus following reset.

**Table 1-4. Default PCI Memory Map**

| PCI Address |           |       |              |

|-------------|-----------|-------|--------------|

| Start       | End       | Size  | Definition   |

| 0000 0000   | 007F FFFF | 8MB   | SDRAM Bank 0 |

| 0080 0000   | 00FF FFFF | 8MB   | SDRAM Bank 1 |

| 0100 0000   | 017F FFFF | 8MB   | SDRAM Bank 2 |

| 0180 0000   | 01FF FFFF | 8MB   | SDRAM Bank 3 |

| 0200 0000   | 0FFF FFFF | 224MB | Unassigned   |

**Table 1-4. Default PCI Memory Map (continued)**

| PCI Address | PCI Address |                 |                              |

|-------------|-------------|-----------------|------------------------------|

| Start       | End         | Size            | Definition                   |

| 1000 0000   | 11FF FFFF   | 32MB            | PCI Bus 1 P2P I/O Space      |

| 1200 0000   | 13FF FFFF   | 32MB            | PCI Bus 1 P2P Memory Space 0 |

| 1400 0000   | 1400 FFFF   | 64KB            | Internal Registers           |

| 1401 0000   | 1BFF FFFF   | 128MB -<br>64KB | Unassigned                   |

| 1C00 0000   | 1C7F FFFF   | 8MB             | Device Port CS0              |

| 1C80 0000   | 1CFF FFFF   | 8MB             | Device Port CS1              |

| 1D00 0000   | 1DFF FFFF   | 16MB            | Device Port CS2              |

| 1E00 0000   | 1FFF FFFF   | 32MB            | Unassigned                   |

| 2000 0000   | 21FF FFFF   | 32MB            | PCI Bus 0 P2P I/O Space      |

| 2200 0000   | 23FF FFFF   | 32MB            | PCI Bus 0 P2P Memory Space 0 |

| 2400 0000   | 25FF FFFF   | 32MB            | PCI Bus 0 P2P Memory Space 1 |

| 2600 0000   | F1FF FFFF   | 3264MB          | Unassigned                   |

| F200 0000   | F3FF FFFF   | 32MB            | PCI Bus 1 P2P Memory Space 1 |

| F400 0000   | FEFF FFFF   | 176MB           | Unassigned                   |

| FF00 0000   | FF7F FFFF   | 8MB             | Device Port CS3              |

| FF80 0000   | FFFF FFFF   | 8MB             | Boot Flash Bank              |

## **MOTLoad's PCI Memory Maps**

MOTLoad's PCI memory map for each PCI domain is shown in the following tables.

Table 1-5. MOTLoad's PCI 0 Domain Memory Map

| PCI 0 Memory Address |           |       |                                 |

|----------------------|-----------|-------|---------------------------------|

| Start End            |           | Size  | Definition                      |

| 0000 0000            | 7FFF FFFF | 2GB   | On-Board SDRAM                  |

| 8000 0000            | DFFF FFFF | 768MB | Local PCI 0 Domain Memory Space |

| F000 0000            | FFFF FFFF | 256MB | Reserved                        |

Table 1-6. MOTLoad's PCI 1 Domain Memory Map

| PCI 1 Memory Address |           |       |                                 |

|----------------------|-----------|-------|---------------------------------|

| Start End            |           | Size  | Definition                      |

| 0000 0000            | 7FFF FFFF | 2GB   | On-Board SDRAM                  |

| E000 0000            | EFFF FFFF | 1GB   | Local PCI 1 Domain Memory Space |

| F000 0000            | FFFF FFFF | 256MB | Reserved                        |

## **PCI I/O Space Maps**

The PCI I/O space map for each PCI domain is shown in the following tables.

Table 1-7. PCI 0 Domain I/O Map

| PCI 0 I/O Address |           |      |                            |

|-------------------|-----------|------|----------------------------|

| Start End         |           | Size | Definition                 |

| 0000 0000         | 007F FFFF | 8MB  | Local PCI Domain I/O Space |

Table 1-8. PCI 1 Domain I/O Map

| PCI 1 I/O Address |           |      |                            |

|-------------------|-----------|------|----------------------------|

| Start End         |           | Size | Definition                 |

| 0000 0000         | 007F FFFF | 8MB  | Local PCI Domain I/O Space |

## System I/O Memory Map

System resources for the MVME5500 board including system control and status registers, NVRAM/RTC, and the 16550 UARTs are mapped into a 1MB address range assigned to device bank 1. The region defined by device bank 1 resides within the GT-64260B device bus register's space listed in Table 1-3 on page 1-6. The memory map is defined in the following table:

Table 1-9. Device Bank 1 I/O Memory Map

| Device Bank1<br>Address Offset | Definition                                |

|--------------------------------|-------------------------------------------|

| 0 0000                         | System Status Register 1                  |

| 0 0001                         | System Status Register 2                  |

| 0 0002                         | System Status Register 3                  |

| 0 0003                         | Reserved                                  |

| 0 0004                         | Presence Detect Register                  |

| 0 0005                         | Software Readable Header/Switch           |

| 0 0006                         | Timebase Enable Register                  |

| 0 0007                         | Geographical Address Register (VME board) |

| 0 0008 - 0 FFFF                | Reserved for future on-board registers    |

| 1 0000 - 1 7FFF                | M48T37V NVRAM/RTC                         |

| 2 0000 - 2 0FFF                | COM1 16550 UART                           |

| 2 1000 - 2 1FFF                | COM2 16550 UART                           |

| 2 4000 - F FFFF                | Reserved (undefined)                      |

## **System Status Register 1**

The MVME5500 board system status register 1 is used to provide board status information and software control of Abort.

REG System Status Register 1 - Offset 0x0 0000 7 5 BIT 6 4 3 2 1 0 **FIELD** FLASH\_BSY\_ SAFE\_START SEL FUSE STAT ABORT BANK RSVD RSVD **OPER** R R R R/W R R R R X X X 1 X X 0 RESET 0

Table 1-10. System Status Register 1

#### **REF CLK**

Reference clock. This bit reflects the current state of the 28.8 KHz reference clock derived from the 1.8432 MHz UART oscillator divided by 64. This clock may be used as a fixed timing reference.

#### BANK\_SEL

Boot Flash bank select. This bit reflects the current state of the boot Flash bank select jumper. A cleared condition indicates that Flash 0 is the boot bank. A set condition indicates that Flash 1 is the boot bank.

#### SAFE START

ENV safe start. This bit reflects the current state of the ENV safe start select jumper. A cleared condition indicates that the ENV settings programmed in NVRAM, VPD, and SPD should be used by the firmware. A set condition indicates that firmware should use the safe ENV settings.

#### ABORT\_

This bit reflects the current state of the on-board abort signal. Writing a 0 at this bit position asserts the abort interrupt output signal, while writing a 1 at this bit position clears the abort interrupt output signal. Reading a 1 at this bit position indicates that the abort switch is deasserted, while reading a 0 at this bit position indicates that the abort switch is asserted.

#### FLASH\_BSY\_

Flash busy. This bit provides the current state of the Flash 0 StrataFlash device status pins. These two open drain output pins are wire ORed. Refer to the appropriate *Intel StrataFlash data sheet* for a description on the function of the status pin.

#### **FUSE\_STAT**

Fuse status. This bit indicates the status of the soldered, on-board fuses (R199 and R188). A cleared condition indicates that one of the fuses is open. A set condition indicates that all fuses are functional.

## System Status Register 2

The MVME5500 board system status register 2 provides board control and status bits.

REG System Status Register 2 - Offset 0x0 0001 7 BIT 6 5 4 3 2 1 0 **FIELD** PCI 0.1 M66EN PCI 1.0\_M66EN PCI 0.0 M66EN TSTAT\_MASK EEPROM\_WP FLASH WP RSVD R/W R/W R R R R **OPER** R/W R/W 1 1 1 1 0 0 X X RESET

Table 1-11. System Status Register 2

#### BD\_FAIL

Board fail. This bit is used to control the board fail LED. A set condition illuminates the front-panel LED and a cleared condition extinguishes the front-panel LED.

#### EEPROM\_WP

EEPROM write protect. This bit is to provide protection against inadvertent writes to the on-board EEPROM devices. Clearing the bit enables writes to the EEPROM devices. Setting this bit write protects the devices. The devices are write protected following a reset.

#### FLASH\_WP

Flash write protect. This bit is used to provide protection against inadvertent writes to both Flash 0 and Flash 1 memory devices. Clearing this bit enables writes to the Flash devices. Setting this bit write protects the devices. This bit is set during reset and must be cleared by the system software to enable writing of the Flash devices.

#### TSTAT\_MASK

Thermostat mask. This bit is used to mask the DS1621 temperature sensor thermostat output. If this bit is cleared, the thermostat output is enabled to generate an interrupt on GPP 3. If the bit is set, the thermostat output is disabled from generating an interrupt.

#### PCI0.1\_M66EN

PCI Bus 0.1 M66EN. This bit reflects the state of the PCI Bus 0.1 M66EN pin. A cleared condition indicates that PCI Bus 0.0 is operating at 33 MHz. A set condition indicates that the bus is operating at 66 MHz. This bit is always cleared on the MVME5500.

#### PCI1.0\_M66EN

PCI Bus 1.0 M66EN. This bit reflects the state of the PCI Bus 1.0 M66EN pin. A cleared condition indicates that PCI Bus 1.0 is operating at 33 MHz. A set condition indicates that the bus is operating at 66 MHz.

#### PCI0.0 M66EN

PCI Bus 0.0 M66EN. This bit reflects the state of the PCI Bus 0.0 M66EN pin. A cleared condition indicates that PCI Bus 0 is operating at 33 MHz. A set condition indicates that the bus is operating at 66 MHz.

## **System Status Register 3**

The MVME5500 board system status register 3 provides the board software-controlled reset functions.

Table 1-12. System Status Register 3

| REG   | System Status Register 3 - Offset 0x0 0002 |                 |      |      |              |      |      |      |  |  |  |

|-------|--------------------------------------------|-----------------|------|------|--------------|------|------|------|--|--|--|

| BIT   | 7                                          | 7 6 5 4 3 2 1 0 |      |      |              |      |      |      |  |  |  |

| FIELD | BRD_RST                                    | RSVD            | RSVD | RSVD | ABT_INT_MASK | RSVD | RSVD | RSVD |  |  |  |

| OPER  | W                                          | R               | R    | R    | R/W          | R    | R    | R    |  |  |  |

| RESET | 0                                          | 0               | 0    | 0    | 1            | 0    | 0    | 0    |  |  |  |

## $BRD_RST$

Board reset. Setting this bit forces a hard reset of the MVME5500 board. This bit clears automatically when the board reset is complete.

#### ABT\_INT\_MASK

Abort interrupt mask. This bit is used to mask the abort interrupt. If this bit is set, the abort interrupt is masked so the abort interrupt is not generated. If the bit is cleared, the abort interrupt may be generated.

## **Presence Detect Register**

The MVME5500 board contains a presence detect register that may be read by the system software to determine the presence of optional devices.

**Table 1-13. Presence Detect Register**

| REG   | Presence Detect Register - Offset 0x0 0004h |      |      |      |      |            |        |        |  |

|-------|---------------------------------------------|------|------|------|------|------------|--------|--------|--|

| BIT   | 7                                           | 6    | 5    | 4    | 3    | 2          | 1      | 0      |  |

| FIELD | RSVD                                        | RSVD | RSVD | RSVD | RSVD | PMC_SPANP_ | PMC2P_ | PMC1P_ |  |

| OPER  | R                                           | R    | R    | R    | R    | R          | R      | R      |  |

| RESET | 1                                           | 1    | 1    | 1    | 1    | X          | X      | X      |  |

#### PMC\_SPANP\_

PMC expansion module present. If set, there is no PMC expansion module installed. If cleared, the PMC expansion module is installed.

#### PMC2P

PMC module 2 present. If set, there is no PMC module installed in position 2. If cleared, the PMC module is installed.

#### PMC1P\_

PMC module 1 present. If set, there is no PMC module installed in position 1. If cleared, the PMC module is installed.

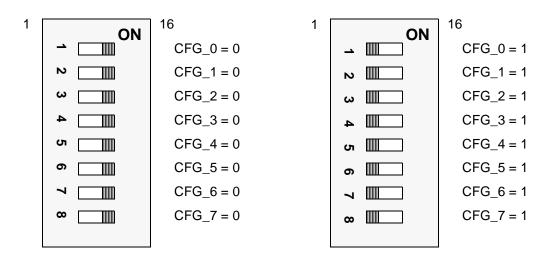

## **Configuration Header/Switch Register (S1)**

The MVME5500 board has an 8-bit header or switch that may be read by the software.

**REG** Configuration Header/Switch Register - Offset 0x0 0005h 7 BIT 6 5 4 3 2 0 **FIELD OPER** R R R R R R R R

X

X

X

X

X

Table 1-14. Configuration Header/Switch Register

#### CFG[7-0]

RESET

X

X

X

Configuration bits 7-0. These bits reflect the position of the switch installed in the software readable header location. A cleared condition indicates that the switch is ON for the header position associated with that bit and a set condition indicates that the switch is OFF.

## **Time Base Enable Register**

The time base enable (TBEN) register provides the means to control the processor's TBEN input.

**REG** TBEN Register- Offset 0x0 0006 7 5 BIT 6 4 3 2 1 0 **FIELD** TBEN0 RSVD RSVD RSVD RSVD RSVD RSVD RSVD

R

0

R

0

R

0

R

0

R/W

1

Table 1-15. TBEN Register

#### TBEN0

**OPER**

RESET

Processor time base enable. When this bit is cleared, the TBEN pin of the processor is driven low. When this bit is set, the TBEN pin is driven high.

## Geographical Address Register (S2)

R

R

0

R

0

This register reflects the inverted states of the geographical address pins at the 5-row, 160-pin P1 connector. Applications not using the 5-row backplane can use a planar switch (same type as the *Configuration Header/Switch Register (S1)* on page 1-17) to assign a geographical address according to the following diagram.

**Note** The switch positions must all be turned off when the MVME5500 is used in a 5-row backplane.

**Table 1-16. Geographical Address Register**

| REG   | Geographical Address Register - 0xFF100007 |               |         |         |         |      |      |         |  |  |  |

|-------|--------------------------------------------|---------------|---------|---------|---------|------|------|---------|--|--|--|

| BIT   | 7                                          | 6 5 4 3 2 1 0 |         |         |         |      |      |         |  |  |  |

| FIELD | VMEGA0_                                    | VMEGA1_       | VMEGA2_ | VMEGA3_ | VMEGA4_ | RSVD | RSVD | VMEGAP_ |  |  |  |

| OPER  | R                                          | R             | R       | R       | R       | R    | R    | R       |  |  |  |

| RESET | X                                          | X             | X       | X       | X       | X    | X    | X       |  |  |  |

16 16 1 1 ON ON  $GAP^* = 0$  $GAP^* = 1$ Not used Not used Not used Not used GA4\* = 0GA4\* = 1GA3\* = 0GA3\* = 1GA2\* = 0GA2\* = 1GA1\* = 0GA1\* = 1GA0\* = 0GA0\* = 1

# COM1 & COM2 Universal Asynchronous Receiver/Transmitter (UART)

COM1 and COM2 are PC16550 Universal Asynchronous Receiver/Transmitter (UART) to provide an asynchronous serial interface for test/debug purposes. To facilitate proper baud rate generation, the frequency of the input clock for the PC16550 UART is fixed at 1.8432 MHz. For additional programming details, refer to the *PC16550 Data Sheet*.

## **Real-Time Clock and NVRAM**

The SGS-Thomson M48T37 is used by the MVME5500 board to provide 32KB of non-volatile static RAM, real-time clock, and watchdog timer functions. The device is accessed as linear memory. Refer to the *MK48T37 Data Sheet* for programming information.

## **ISA Local Resource Bus**

The ISA local resources exist *only* if an IPMC712/761 module is mounted on the MVME5500. Refer to the *IPMC712/761 I/O Module Installation and Use*, listed in Appendix B, *Related Documentation*.

## Introduction

This chapter includes additional programming information for the MVME5500 single-board computer. Items discussed include:

□ PCI Configuration Space and IDSEL Mapping on page 2-1

□ Interrupt Controller on page 2-3

□ Two-Wire Serial Interface on page 2-5

□ GT-64260B Initialization on page 2-7

□ GT-64260B GPP Configuration on page 2-7

□ GT-64260B Reset Configuration on page 2-9

□ GT-64260B Device Controller Bank Assignments on page 2-11

□ System Clock Generators on page 2-13

□ VPD and User Configuration EEPROMs on page 2-14

□ Temperature Sensor on page 2-14

□ Flash Memory on page 2-14

□ PCI Arbitration Assignments on page 2-15

□ Other Software Considerations on page 2-15

## **PCI Configuration Space and IDSEL Mapping**

Each PCI device has an associated address line connected via a resistor to its IDSEL pin for configuration space accesses. Table 2-1 shows the IDSEL assignments for the PCI devices on each of the PCI buses on the MVME5500 board along with the corresponding interrupt assignment to the general-purpose port (GPP) pins. Refer to the *GT-64260B System Controller for PowerPC Processors Data Sheet* and the *PCI 6154 (HB2) PCI-to-PCI Bridge Data Book*, both listed in Appendix B, *Related*

2-1

*Documentation*, for details on generating configuration cycles on each of the PCI buses.

**Table 2-1. IDSEL Mapping for PCI Devices**

| PCI | Device          | PCI<br>AD | Physical PCI                                                                                                                                             | Device INT# to GPP Interrupt<br>Input |                                                     |                             |       |  |

|-----|-----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------|-----------------------------|-------|--|

| Bus | Number Field    | Line      | Device                                                                                                                                                   | INTA#                                 | INTB#                                               | INTC#                       | INTD# |  |

| 0.0 | 0b0_0001        | AD11      | IPMC                                                                                                                                                     | 11                                    |                                                     |                             |       |  |

|     | 0b0_0110        | AD16      | PMC 1<br>(J11,12,13,14)                                                                                                                                  | 8                                     | 9                                                   | 10                          | 11    |  |

|     | 0b0_0111        | AD17      | PMC 1 IDSEL B                                                                                                                                            |                                       |                                                     |                             |       |  |

|     | 0b0_1010        | AD20      | HiNT PCI 6154<br>Bridge                                                                                                                                  |                                       |                                                     |                             |       |  |

|     | 0b1_0101        | AD31      | GT-64260B PCI<br>Bridge                                                                                                                                  |                                       |                                                     |                             |       |  |

| 0.1 | 1 0b0_0000 AD16 |           | CA91C142D VME<br>VLINT0                                                                                                                                  | 12                                    |                                                     |                             |       |  |

|     |                 |           | CA91C142D VME<br>VLINT1                                                                                                                                  | 13                                    |                                                     |                             |       |  |

|     |                 |           | CA91C142D VME<br>VLINT2                                                                                                                                  | 14                                    |                                                     |                             |       |  |

|     |                 |           | CA91C142D VME<br>VLINT3                                                                                                                                  | 15                                    |                                                     |                             |       |  |

|     | 0b0_0100        | AD20      | PMC Expansion                                                                                                                                            | 12                                    | 13                                                  | 14                          | 15    |  |

|     |                 |           | Note Device-specific introuting is established on to board. Refer to the PMC Adapter Carrier Board Is and Use manual, listed in B, Related Documentation |                                       | ed on the F<br>PMCspan<br>oard Insta<br>isted in Ap | PMCspan<br>n PMC<br>llation |       |  |

**Device INT# to GPP Interrupt** PCI Input PCI Device AD **Physical PCI** INTA# INTB# INTC# INTD# Bus Number Field Line **Device** 1.0 0b0 0110 PMC 2 16 17 18 19 AD16 (J21,22,23,24) 0b0 0111 AD17 PMC 2 IDSEL B 0b0 1010 82C544 Ethernet 1 20 AD20

GT-64260B PCI

Bridge

**Table 2-1. IDSEL Mapping for PCI Devices (continued)**

## **Interrupt Controller**

AD31

0b1 0101

The MVME5500 uses the GT-64260B interrupt controller to handle interrupts internal to the GT-64260B, as well as the external interrupt sources. The GT-64260B has a limited number of directly triggerable interrupt inputs. Each of the GPP pins can be configured for an interrupt input, but the inputs are combined internally in groups of eight inputs (one for each byte lane) for one interrupt source. Therefore, interrupt inputs in each byte lane are essentially shared. Currently defined external interrupting devices and GPP interrupt assignments are shown in Table 2-2.

The GT-64260B has one dedicated processor interrupt output, CPUINT\_, which is connected to the primary processor CPU0 INT\_L input. Refer to

the *GT-64260B System Controller for PowerPC Processors Data Sheet*, listed in Appendix B, *Related Documentation*, for details.

Table 2-2. GT-64260B External GPP Interrupt Assignments

| GPP<br>Group | GPP# | Edge/<br>Level | Polarity | Interrupt Source                          |

|--------------|------|----------------|----------|-------------------------------------------|

| 0            | 0    | Level          | High     | COM1    COM2                              |

|              | 1    | Level          | Low      | Not Used. Pulled High.                    |

|              | 2    | Level          | Low      | Abort Switch                              |

|              | 3    | Level          | Low      | RTC    Thermostat Output                  |

|              | 4    | Level          | Low      | Not Used. Pulled high, tied to GPP27.     |

|              | 5    | Level          | Low      | Not Used. Pulled high, tied to GPP28.     |

|              | 6    | Level          | Low      | GT-64260B WDMNI Interrupt. Tied to GPP24. |

|              | 7    | Level          | Low      | LXT971A Interrupt (10/100Mbit PHY)        |

| 1            | 8    | Level          | Low      | PMC 1 Interrupt INT A                     |

|              | 9    | Level          | Low      | PMC 1 Interrupt INT B                     |

|              | 10   | Level          | Low      | PMC 1 Interrupt INT C                     |

|              | 11   | Level          | Low      | PMC 1 Interrupt INT D    IPMC INT         |

|              | 12   | Level          | Low      | VME Interrupt VLINT0                      |

|              | 13   | Level          | Low      | VME Interrupt VLINT1                      |

|              | 14   | Level          | Low      | VME Interrupt VLINT2                      |

|              | 15   | Level          | Low      | VME Interrupt VLINT3                      |

Table 2-2. GT-64260B External GPP Interrupt Assignments (continued)

| GPP<br>Group | GPP# | Edge/<br>Level | Polarity | Interrupt Source                             |

|--------------|------|----------------|----------|----------------------------------------------|

| 2            | 16   | Level          | Low      | PMC 2 Interrupt INT A                        |

|              | 17   | Level          | Low      | PMC 2 Interrupt INT B                        |

|              | 18   | Level          | Low      | PMC 2 Interrupt INT C                        |

|              | 19   | Level          | Low      | PMC 2 Interrupt INT D                        |

|              | 20   | Level          | Low      | 82544 Interrupt                              |

|              | 21   | Level          | Low      | Not Used. Pulled High.                       |

|              | 22   | Level          | Low      | Not Used. Pulled High.                       |

|              | 23   | Level          | Low      | Not Used. Pulled High.                       |

| 3            | 24   |                |          | Watchdog Timer NMI Output WDNMI# to GPP6     |

|              | 25   |                |          | Watchdog Timer Expired Output WDE#           |

|              | 26   |                |          | GT-64260B SROM Initialization Active InitAct |

|              | 27   | Level          | Low      | Not Used. Pulled high, tied to GPP4.         |

|              | 28   |                |          | Not Used. Pulled high, tied to GPP5.         |

|              | 29   |                |          | Optional External PPC Bus Arbiter BG1 Enable |

|              | 30   |                |          | Unused. Pulled High.                         |

|              | 31   |                |          | Unused. Pulled High.                         |

#### **Two-Wire Serial Interface**

A two-wire serial interface for the MVME5500 board is provided by an I2C compatible serial controller integrated into the GT-64260B system controller. The I2C serial controller provides two basic functions. The first function is to provide GT-64260B register initialization following a reset. The GT-64260B can be configured (by jumper setting) to automatically read data out of a serial EEPROM following a reset and initialize any number of internal registers. In the second function, the controller is used by the system software to read the contents of the VPD EEPROM

contained on the MVME5500 board, along with the SPD EEPROMs, to further initialize the memory controller and other interfaces. For additional details regarding the GT-64260B two-wire serial controller operation, refer to the *GT-64260B System Controller for PowerPC Processors Data Sheet*, listed in Appendix B, *Related Documentation*.

Table 2-3 shows the I2C devices used for the MVME5500 and the assigned device IDs.

Table 2-3. I2C Bus Device Addressing

| Device Function                           | Size    | Device<br>Address<br>(A2A1A0) | I2C BUS<br>Address | Notes |

|-------------------------------------------|---------|-------------------------------|--------------------|-------|

| Memory SPD (On-board. Banks A and B.)     | 256 x 8 | 000b                          | \$A0               | 1, 2  |

| Memory SPD (On mezzanine. Banks C and D.) | 256 x 8 | 001b                          | \$A2               | 1     |

| IPMC VPD                                  | 256 x 8 | 010b                          | \$A4               |       |

| GT-64260B Fixed Initialization            | 256 x 8 | 011b                          | \$A6               | 2     |

| Configuration VPD                         | 8K x 8  | 100b                          | \$A8               | 2, 3  |

| User VPD                                  | 8K x 8  | 101b                          | \$AA               | 2, 3  |

| Not Used                                  | NA      | 110b                          | \$AC               |       |

| Not Used                                  | NA      | 111b                          | \$AE               |       |

| DS1621 Temperature Sensor                 | NA      | 000b                          | \$90               |       |

#### Notes

- 1. Each SPD defines the physical attributes of each bank or group of banks, that is, if both banks of a group are populated, they will be the same speed and memory size.

- 2. This device can be write-protected by either setting the EEPROM\_WP bit of SSR2 or by placing a jumper on the EEPROM write protect header. The hardware jumper mechanism always takes precedence over the software setting. For 8KB sized parts, only the upper 2KB are write-protectable.

- 3. This is a 2-byte address serial EEPROM (AT24C64).

### **GT-64260B** Initialization

Serial EEPROM devices are provided to support optional initialization of the GT-64260B (enabled by an on-board jumper). Using the SROM initialization method, any of the GT-64260B internal registers or other system components (that is, devices on the PCI bus) can be initialized. Initialization takes place by sequentially reading 8-byte address/data pairs from the SROM and writing the 32-bit data to the decoded 32-bit address until the data pattern matching the last serial data item register is read for the SROM (default value = 0xffffffff). The on-board reset logic keeps the processor reset asserted until this initialization process is completed.

### **GT-64260B GPP Configuration**

The GT-64260B contains a 32-bit GPP. The GPP pins can be configured as general-purpose I/O pins, as external interrupt inputs, or as specific control/status pins for one of the GT-64260B internal devices. After reset, all GPP pins default to general-purpose inputs. Software must then configure each of the pins for the desired function. The following table defines the function assigned to each GPP pin on the MVME5500 board.

Table 2-4. GT-64260B GPP Pin Function Assignments

| <b>GPP Number</b> | Input/Output | Function                                  |

|-------------------|--------------|-------------------------------------------|

| 0                 | I            | COM1/COM2 interrupts (ORed)               |

| 1                 | I            | Not Used. Pulled High.                    |

| 2                 | I            | Abort Interrupt                           |

| 3                 | I            | RTC and Thermostat Interrupts (ORed)      |

| 4                 | О            | Not Used. Pulled high, tied to GPP27.     |

| 5                 | I            | Not Used. Pulled high, tied to GPP28.     |

| 6                 | I            | GT-64260B WDMNI Interrupt. Tied to GPP24. |

| 7                 | I            | LXT971A Interrupt (10/100Mbit PHY)        |

| 8                 | I            | PMC 1 Interrupt INT A                     |

## Table 2-4. GT-64260B GPP Pin Function Assignments (continued)

| GPP Number | Input/Output | Function                                      |

|------------|--------------|-----------------------------------------------|

| 9          | I            | PMC 1 Interrupt INT B                         |

| 10         | I            | PMC 1 Interrupt INT C                         |

| 11         | I            | PMC 1 Interrupt INT D/IPMC INT                |

| 12         | I            | VME Interrupt 0                               |

| 13         | I            | VME Interrupt 1                               |

| 14         | I            | VME Interrupt 2                               |

| 15         | I            | VME Interrupt 3                               |

| 16         | I            | PMC 2 Interrupt INT A                         |

| 17         | I            | PMC 2 Interrupt INT B                         |

| 18         | I            | PMC 2 Interrupt INT C                         |

| 19         | I            | PMC 2 Interrupt INT D                         |

| 20         | I            | 82544 Interrupt                               |

| 21         | I            | Not Used. Pulled High.                        |

| 22         | I            | Not Used. Pulled High.                        |

| 23         | I            | Not Used. Pulled High.                        |

| 24         | 0            | Watchdog Timer NMI Output WDNMI# to GPP6      |

| 25         | 0            | Watchdog Timer Expired Output WDE#            |

| 26         | 0            | GT-64260B SROM Initialization Active InitAct  |

| 27         | I            | Not Used. Pulled high, tied to GPP4.          |

| 28         | 0            | Not Used. Pulled high, tied to GPP5.          |

| 29         | 0            | Optional external PPC Bus Arbiter BG1 Enable. |

| 30         | I            | Not Used. Pulled High.                        |

| 31         | I            | Not Used. Pulled High.                        |

### GT-64260B Reset Configuration

The GT-64260B supports two methods of device initialization following reset:

- ☐ Pins sampled on the deassertion of reset

- ☐ Partial pin sample on deassertion of reset plus serial ROM initialization via the I2C bus

The MVME5500 board supports both options listed above. An on-board jumper setting is used to select the option. If the pin-sample-only method is selected, then states of the various pins on the device AD bus are sampled when reset is deasserted to determine the desired operating modes. Table 2-5 on page 2-10 describes the configuration options. Combinations of pullups, pulldowns, and jumpers are used to set the options. Some options are fixed and some are selectable at build time by installing the proper pullup/pulldown resistor. Finally, some options may be selected using on-board jumpers.

Using the SROM initialization method, any of the GT-64260B internal registers or other system components (that is, devices on the PCI bus) can be initialized. Initialization takes place by sequentially reading 8-byte address/data pairs from the SROM and writing the 32-bit data to the decoded 32-bit address until the last serial data item of 0xffffffff is read. If the SROM initialization option is selected, the following pins are still sampled to determine certain operating parameters:

- $\Box$  AD(1) SROM byte offset width

- $\Box$  AD(3:2) SROM address

- $\Box$  AD(4) CPU endianess

- $\Box$  AD(30:28) PLL settings

- $\Box$  AD(31) CPU interface voltage

Table 2-5. GT-64260B Power-Up Configuration Settings

| Device AD<br>Bus Signal | Select<br>Option | Default<br>Power-Up<br>Setting | Description                      | State | of Bit vs. Function                       |

|-------------------------|------------------|--------------------------------|----------------------------------|-------|-------------------------------------------|

| AD[0]                   | Jumper           | X                              | SROM Initialization              | 0     | No SROM<br>Initialization                 |

|                         |                  |                                |                                  | 1     | SROM Initialization<br>Enabled            |

| AD[1]                   | Resistor         | 0                              | SROM Byte Offset<br>Width        | 0     | Up to 8 Bits                              |

| AD[3:2]                 | Resistors        | 11                             | SROM Device<br>Address           | 11    | 1010011 (\$A6)                            |

| AD[4]                   | Fixed            | 0                              | CPU Data Endianess               | 0     | Must be Pulled Down                       |

| AD[5]                   | Fixed            | 1                              | CPU Interface Clock              | 1     | CPU Interface<br>Synchronous with<br>TClk |

| AD[6]                   | Jumper           | Х                              | CPU Bus                          | 0     | 60x Bus Mode                              |

|                         |                  |                                | Configuration                    | 1     | MPX Bus Mode                              |

| AD[8]                   | Resistor         | 1                              | Internal 60x Bus<br>Arbiter      | 1     | Internal Arbiter<br>Enabled               |

| AD[9]                   | Fixed            | 0                              | Multiple GT-64260B<br>Support    | 0     | Not Supported                             |

| AD[11:10]               | Fixed            | 11                             | Multiple GT-64260B<br>Address ID | 11    | GT Responds to CPU<br>Address A[5:6] = 11 |

| AD[12]                  | Fixed            | 0                              | SDRAM UMA                        | 0     | Not Supported                             |

| AD[13]                  | Fixed            | 0                              | UMA Device Type                  | 0     | UMA Master                                |

| AD[15:14]               | Fixed            | 10                             | BootCS* Device<br>Width          | 10    | 32 Bits                                   |

| AD[16]                  | Resistor         | 1                              | PCI Retry                        | 1     | Enable                                    |

Table 2-5. GT-64260B Power-Up Configuration Settings (continued)

| Device AD<br>Bus Signal | Select<br>Option | Default<br>Power-Up<br>Setting | Description                       | State o | of Bit vs. Function |

|-------------------------|------------------|--------------------------------|-----------------------------------|---------|---------------------|

| AD[17]                  | Fixed            | 0                              | PCI_0 Expansion<br>ROM            | 0       | Not Supported       |

| AD[18]                  | Fixed            | 0                              | PCI_1 Expansion<br>ROM            | 0       | Not Supported       |

| AD[22:19]               | Fixed            | 0000                           | Reserved                          | 0000    | Must be Pulled Down |

| AD[23]                  | Fixed            | 1                              | SDClkIn/<br>SDClkOut Select       | 1       | SDClkIn             |

| AD[24]                  | Resistor         | 1                              | Internal Space Default<br>Address | 1       | 0xf100.0000         |

| AD[27:25]               | Fixed            | 000                            | Reserved                          | 000     | Must be Pulled Down |

| AD[28]                  | Resistor         | 0                              | PLL Tune                          | 0       | Tuning Option 0     |

| AD[29]                  | Resistor         | 0                              | PLL Divider                       | 0       | Divider Option 0    |

| AD[30]                  | Resistor         | 0                              | PLL Bypass                        | 0       | PLL Enabled         |

| AD[31]                  | Fixed            | 0                              | CPU Interface Voltage             | 0       | 2.5V                |

# **GT-64260B Device Controller Bank Assignments**

The MVME5500 board uses three of the GT-64260B device controller banks for interfacing to various devices. The following tables define the device bank assignments and the programmable device bank timing parameters required for each of the banks used. Note that all device bank

timing parameters, except *BAdrSkew*, have an extension bit that forms the most significant bit of the timing parameter.

**Table 2-6. Device Bank Assignments**

| Device Bank | Data Width | Function                                            | Note |

|-------------|------------|-----------------------------------------------------|------|

| 0           | 32 bit     | Flash 0 Soldered Flash or Flash<br>1 Soldered Flash | 1    |

| 1           | 8 bit      | I/O Devices                                         |      |

| 2           | NA         | Not used                                            |      |

| 3           | NA         | Not used                                            |      |

| Boot        | 32 bit     | Flash 1 Soldered Flash or Flash 0 Soldered Flash    | 1    |

**Note** 1. Determined by Flash boot bank select jumper.

**Table 2-7. Device Bank Timing Parameters**

|                |                                  |                          | Device Bank Timing Parameter Min. Value |                       |                    |                  |                    |          |

|----------------|----------------------------------|--------------------------|-----------------------------------------|-----------------------|--------------------|------------------|--------------------|----------|

| Device<br>Bank | GT-64260B<br>Tclk Clock<br>Freq. | Acc2FirstExt - Acc2First | Acc2NextExt - Acc2Next                  | TurnOff Ext - TurnOff | ALE2WrExt - ALE2Wr | WrLowExt - WrLow | WrHighExt - WrHigh | BAdrSkew |

| Flash 0        | 100 MHz                          | 1 - 1                    | 0 - 3                                   | 0 - 6                 | 0 - 3              | 0 - 7            | 0 - 4              | 0        |

| (150 ns)       | 133 MHz                          | 1 - 6                    | 0 - 4                                   | 0 - 8                 | 0 - 3              | 1 - 2            | 0 - 5              | 0        |

| Flash 0        | 100 MHz                          | 0 - e                    | 0 - 3                                   | 0 - 6                 | 0 - 3              | 0 - 7            | 0 - 4              | 0        |

| (120 ns)       | 133 MHz                          | 1 - 2                    | 0 - 4                                   | 0 - 8                 | 0 - 3              | 1 - 2            | 0 - 5              | 0        |

Device Bank Timing Parameter Min. Value Acc2FirstExt - Acc2First Acc2NextExt - Acc2Next ALE2WrExt - ALE2Wr TurnOff Ext - TurnOff WrHighExt - WrHigh WrLowExt - WrLow **BAdrSkew** GT-64260B **Device** Tclk Clock Bank Freq. Flash 0 100 MHz 0 - c0 - 30 - 6 0 - 30 - 70 - 40 (100 ns)133 MHz 1 - 0 0 - 40 - 80 - 31 - 2 0 - 5 0 Device 0 - 5 0 - 3 0 100 MHz 0 - c0 - a1 - 00 - 4 Bank1 0 - 6 133 MHz 1 - 0 0 - e 0 - 7 0 - 3 1 - 3 0 I/O 0 - 9 0 - 3 0 - 3 0 Flash 1 100 MHz 0 - b0 - 4 0 - 3 (90 ns) 0 - 4 0 - 30 - 50 133 MHz 0 - e0 - c0 - 4

**Table 2-7. Device Bank Timing Parameters (continued)**

**Note** Flash 0 contains 100 ns, 120 ns, or 150 ns StrataFlash devices. Device speed can be determined from VPD.

# System Clock Generators

The system clock generator functions generate and distribute all of the clocks required for system operation. The clocks for the processor, memory, and PCI devices consist of a clock tree derived from a 66 MHz oscillator and a series of PLL clock generators. The clock tree is designed in such a manner as to maintain the strict edge-to-edge jitter and low clock-to-clock skew required by these devices. Additional clocks required by individual devices are generated near the devices using individual oscillators.

### VPD and User Configuration EEPROMs

The MVME5500 board contains an Atmel AT24C64 vital product data (VPD) EEPROM containing configuration information specific to the board. Typical information that may be present in the VPD is: manufacturer, board revision, build version, date of assembly, memory present, options present, L3 cache information, etc. A second AT24C64 device is available for user data storage.

### **Temperature Sensor**

The MVME5500 board contains a Maxim DS1621 digital temperature sensor with an I2C serial bus interface. This device may be used to provide a measure of the ambient temperature of the board.

### Flash Memory

The MVME5500 contains two banks of Flash memory accessed via the device controller contained within the GT-64260B. Flash 1 consists of two soldered 32Mb devices (E28F320J3A) to give a minimum of 8MB Flash memory. Flash 0 consists of two Intel StrataFlash 3.3 volt devices, configured to operate in 16-bit mode, to form a 32-bit Flash port. This bank contains 64Mb devices (E28F128J3A) for 32MB of Flash.

There is a Flash boot bank select jumper on board, which selects either Flash 0 or Flash 1 as the boot bank. No jumper or a jumper installed between pins 1 and 2 selects Flash 0 as the boot bank. A jumper installed between pins 2 and 3 selects Flash 1 as the boot bank.

# **PCI Arbitration Assignments**

PCI arbitration for PCI Bus 0.0 and PCI Bus 1.0 is handled using logic implemented in PLDs. These arbiters use a rotating priority scheme for fairness and bus parking will always be on the GT-64260B. There are no software programmable modes to these arbiters.

PCI arbitration for PCI Bus 0.1 is provided by the HiNT PCI 6154 secondary side arbiter.

**Table 2-8. PCI Arbiter Assignments**

| PCI Bus<br>Number | REQ/GNT<br>Pair | PCI Device                           |

|-------------------|-----------------|--------------------------------------|

| 0.0               | 0               | GT-64260B Host                       |

|                   | 1               | PMC Req 1                            |

|                   | 2               | PMC Req 2                            |

|                   | 3               | PCI-to-PCI Bridge<br>(HiNT PCI 6154) |

|                   | 4               | Not Used                             |

| 0.1               | 0               | PCI/PMC Expansion                    |

|                   | 1               | VME Controller                       |

| 1.0               | 0               | GT-64260B Host                       |

|                   | 1               | PMC Req 1                            |

|                   | 2               | PMC Req 2                            |

|                   | 3               | 82544                                |

|                   | 4               | Not Used                             |

#### Other Software Considerations

The following subsections discuss software aspects of the CPU bus, processor, and cache that can have an influence on the MVME5500.

#### **CPU Bus Mode**