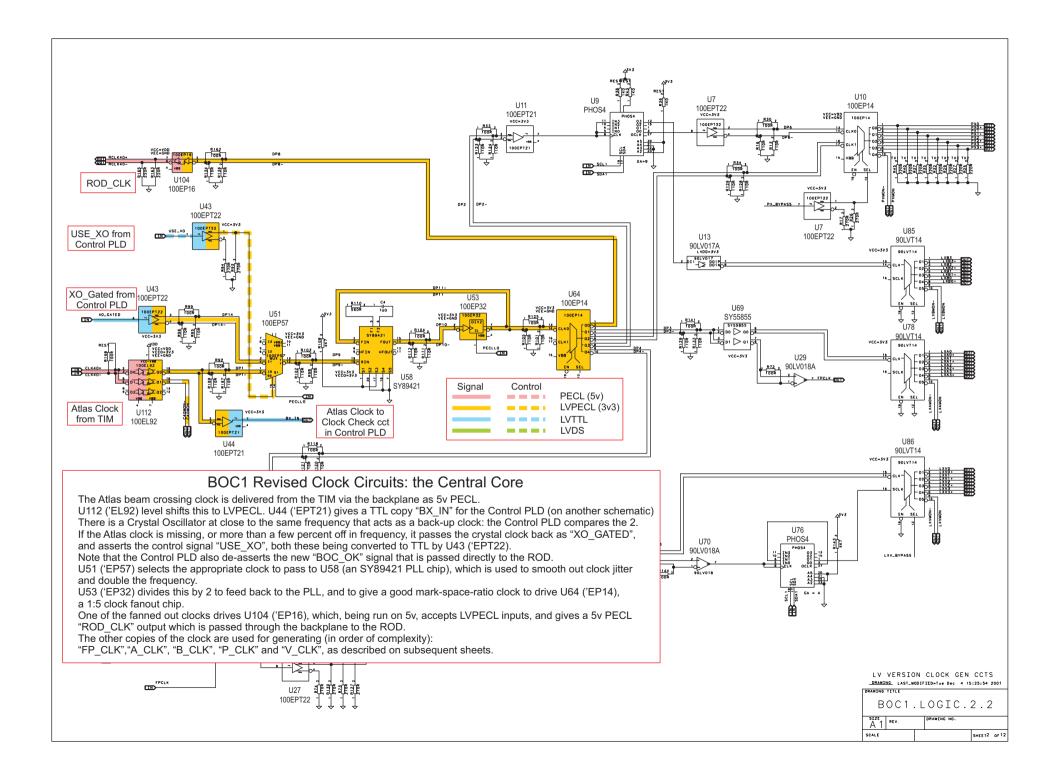

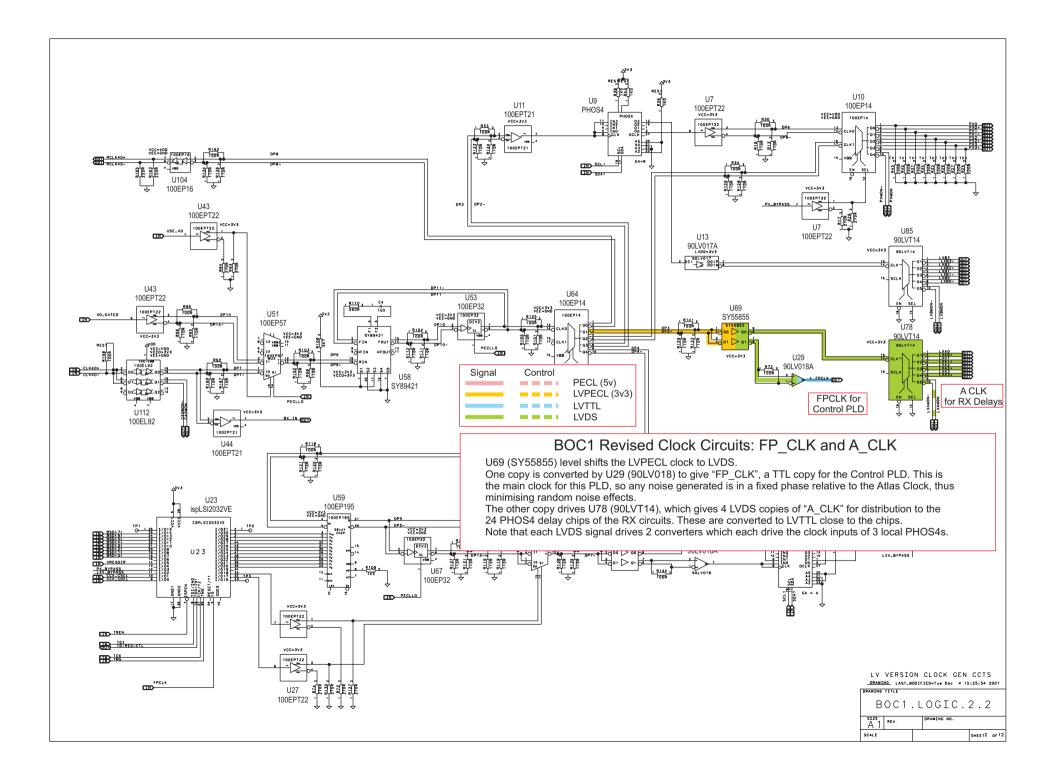

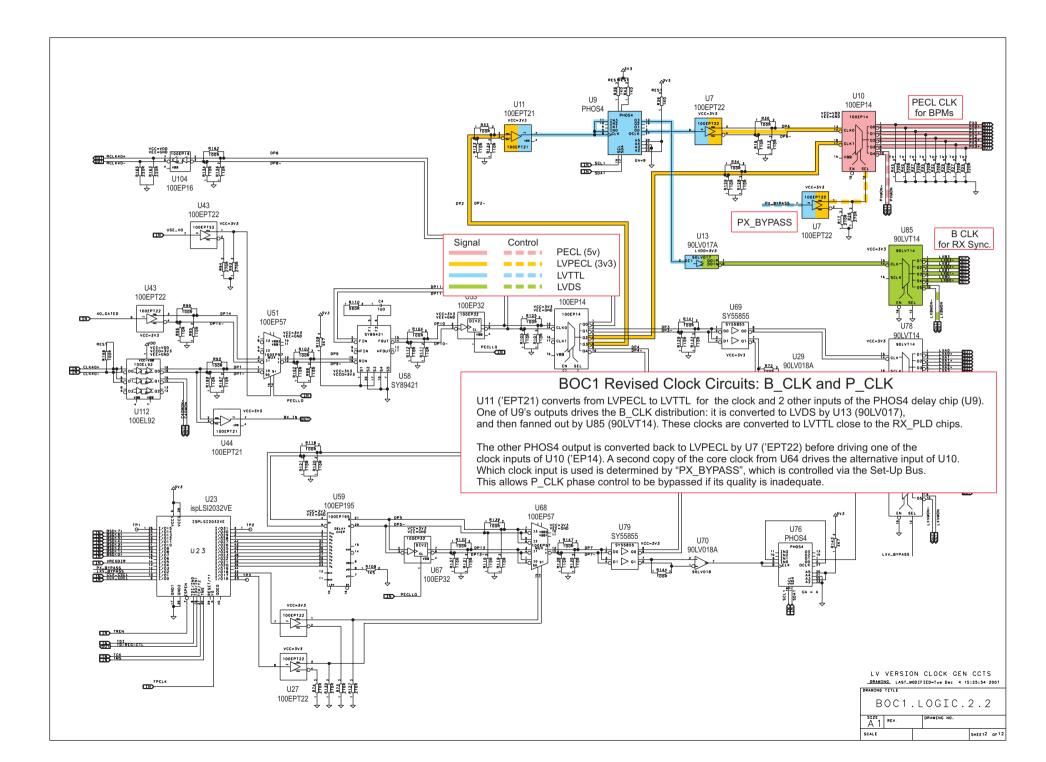

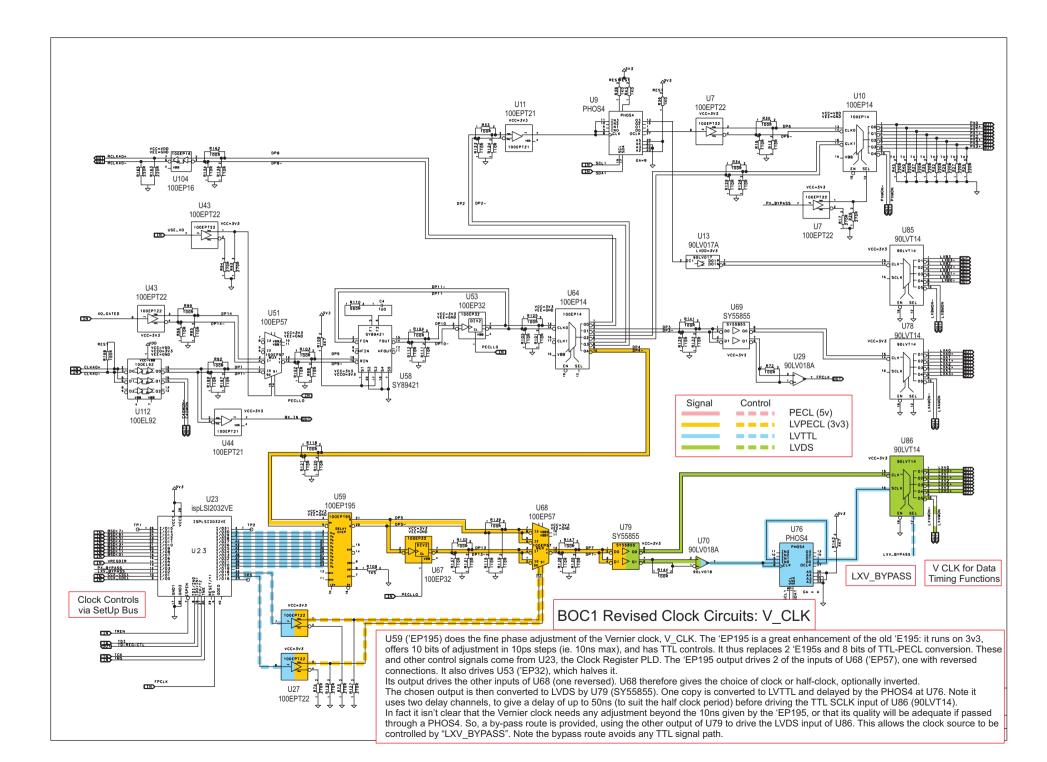

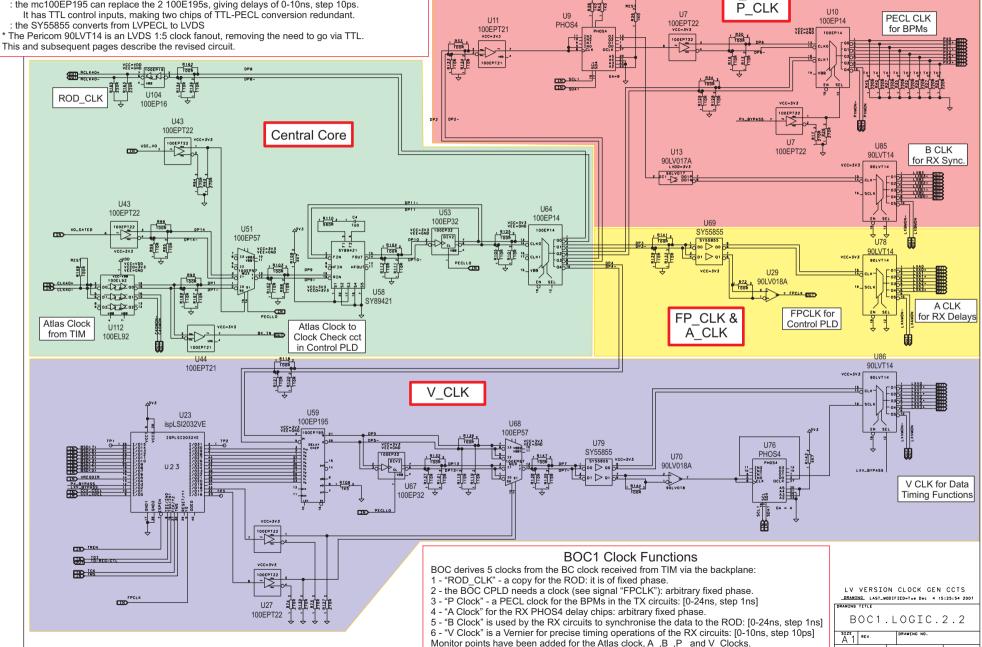

## BOC1 Revised Clock Circuits: the Why and the What

The BOC1 "Run-Thru" meeting of 15-Nov-01 concentrated on the clock circuits. Two points arose: \* the need for a dedicated signal to ROD to indicate that the fall-back clock was in use, and ... \* the timing uncertainties introduced by the TTL devices in the circuit The first point has been dealt with; the second led to a circuit rethink that uncovered a number of new PECL and LVDS devices that have allowed us to overhaul the circuit completely.

\* The ECLinPS Pro "100EP" devices from ON Semi and Micrel-Synergy offer:

- : 3v3/5v operation, removing the need to buffer the PHOS4s

- : the mc100EP195 can replace the 2 100E195s, giving delays of 0-10ns, step 10ps. It has TTL control inputs, making two chips of TTL-PECL conversion redundant.

B CLK &

SCALE

SHEET2 OF 12