RCE / HSIO Distribution for ATLAS Applications (May/2016)

General Information

The generic high bandwidth DAQ development with RCE concept,base on the System on Chip (SoC) technology

offered by the XILINX ZYNQ-7000

series, has now served various ATLAS readout needs such as

IBL readout for stave/system/installation

tests with Gen-1 RCEs, the muon CSC readout

replacement commissioined during LS1 as a first ATCA deployment in ATLAS, and the more recent HSIO-II based

readout of AFP in ATLAS

datataking.

This call for shared production is more oriented towards ITk upgrade needs with HSIO-2 based readout

in particular to serve test stands (e.g.

CERN SR1 setup), and test beams (e.g.

SLAC ESTB setup). The general information and support for RCE based development in ATLAS now have updated

documentations in the

RCE Development Lab Twiki.

Hardware Components

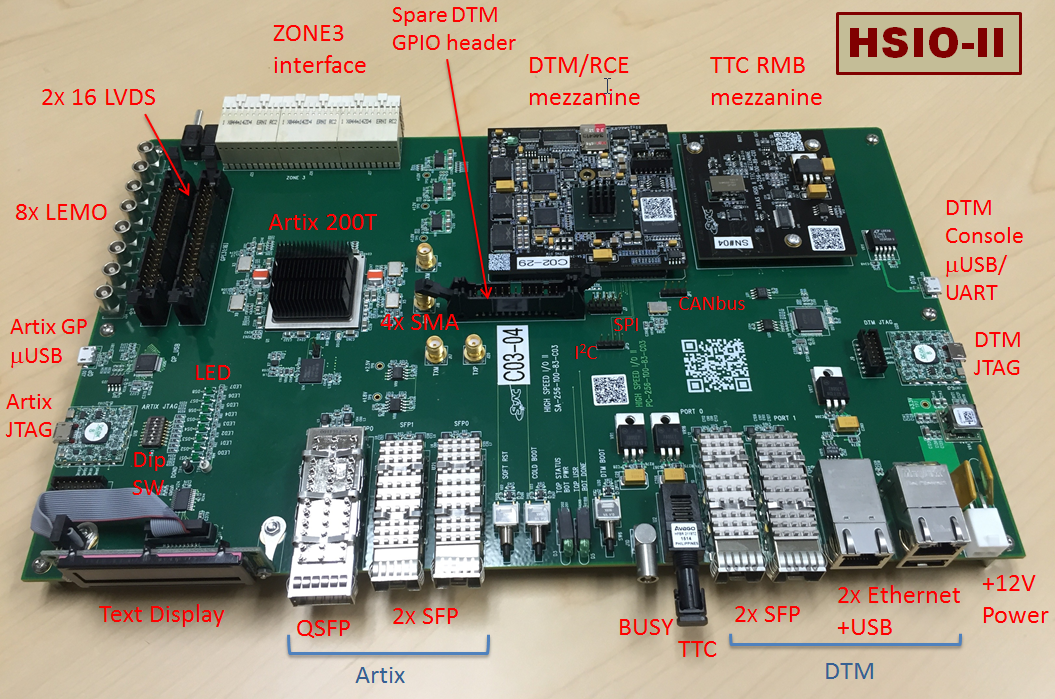

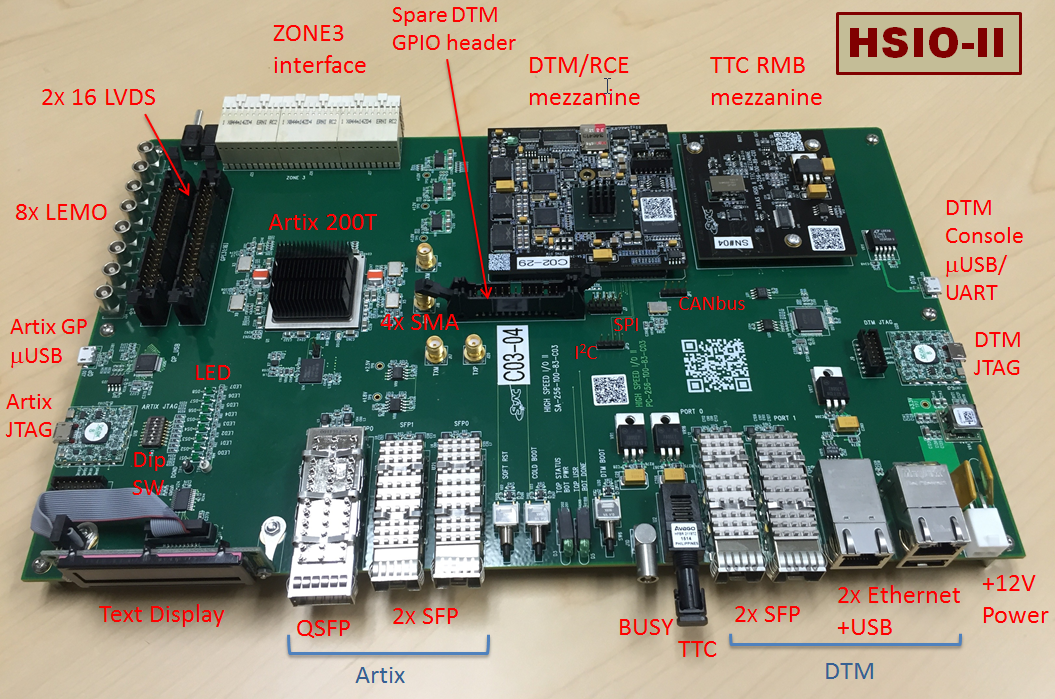

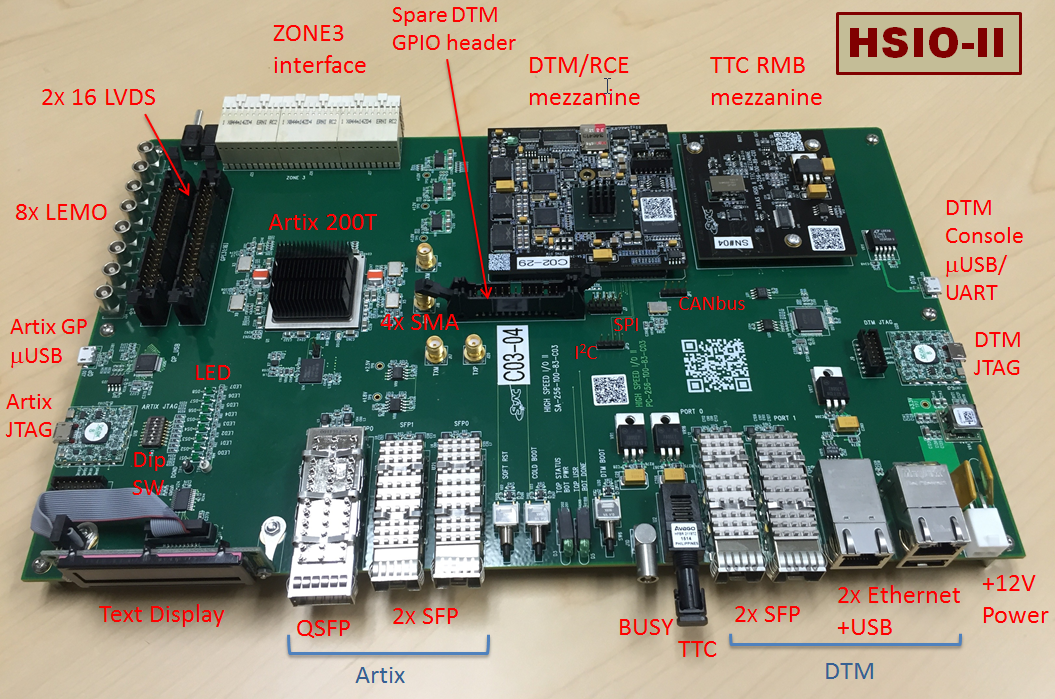

The primary target for this round of production is to meet additional requests for HSIO-II based readout

setups for ITk R&D, following the

Mar/2015 production round. The HSIO-II upgrade combines both the I/O versatility of original HSIO and

the RCE programmability in the form of a DTM mezzanine card running Arch-Linux, for a self-contained compact

bench-top DAQ system. A TTC mezzanine is also incldued. Further details of the HSIO-II platform is documented

in the current

Gen-3 RCE instructions Twiki.

HSIO-II has an ATCA styled user defined P3 connector that can work with various flavors of interface/adaptor

boards like an ATCA RTM. The known variations of interface types:

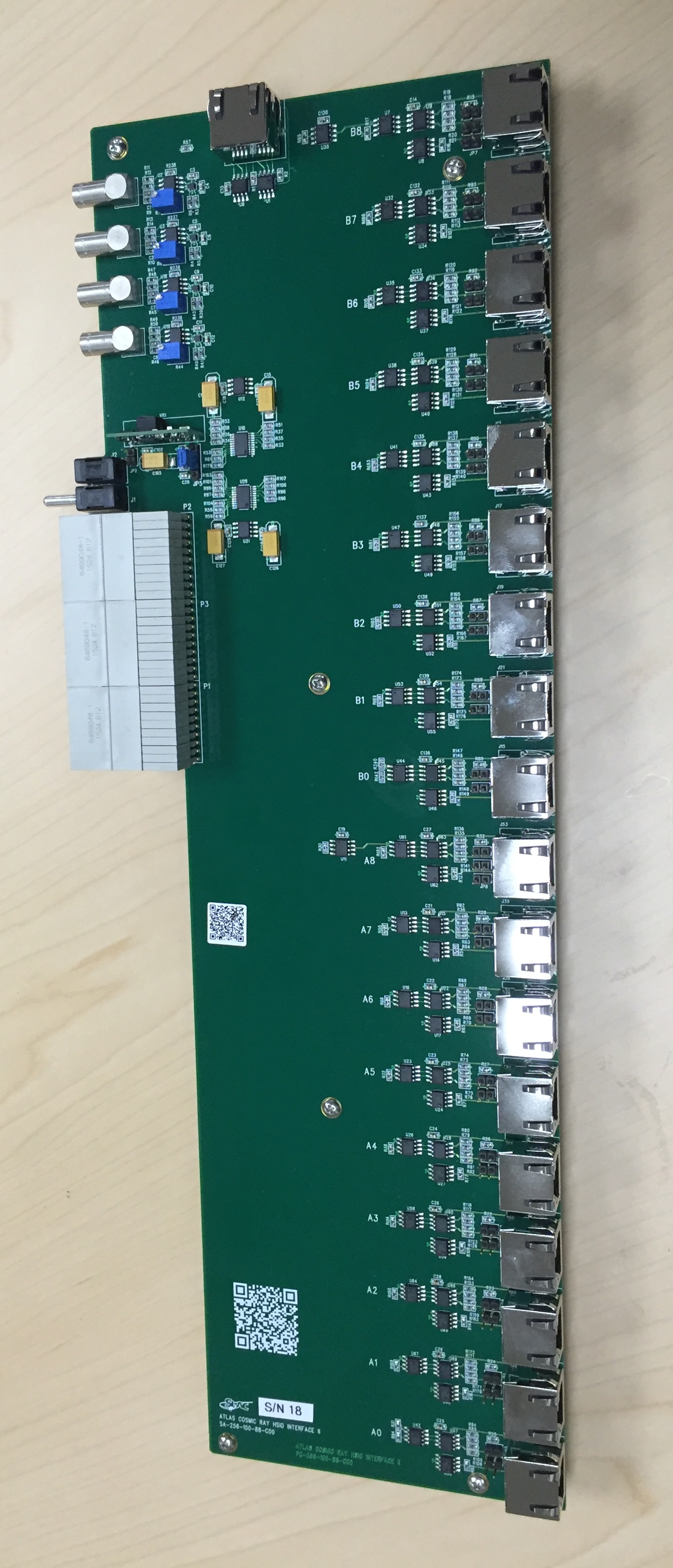

- Pixel Interface: the current version of this is with 18 RJ45 connectors following the standard IBL

and ITk pixel test card interface. We will only offer production of this interface for this round. HSIO-II is

also backward compatible with various other existing types of pixel/IBL interfaces produced previously,

with matching firmware/software options to utilize them (if you can get hold of one yourself).

- Strip Stave: HSIO-II is also backward compatible to the old stave-09 Si-strip test setup from the

hardware point of view to utilize existing stave-09 interfaces. However, some firmware porting still needs to

be done to enable that. The interafce to the next generation of stave test setup is not yet defined so that we

will not offer producing strip stave interface until the new interafce is defined in future rounds.

- No interface: the various interface boards are mostly aimed at collecting many slower E-links from

the older and current generation of devices to combine them into smaller number of faster fiber links on

HSIO-II. Many future ITk R&D devices will be more likely to have faster and optical links the HSIO-II can talk

to directly from the main board without the RTM styled interace. This includes GBT test boards with Versatile

Links and possibly some ITk CMOS front end test boards with optical links.

The distribution will not include any transceivers for the high speed links given the potentially very

different usage at diffferent places. The HSIO-II main board is powered with a 12V AC/DC laptop supply that

will be included in the delivered package, but without the wall plug cable which is country dependent.

Further orders of the ATCA based COB readout components can still be considered and included in the request

form, but we cannot formally accept the order until the situation is clearer when the order can join a larger

shared production round with other projects and the production time will be longer compared to HSIO-II.

Details and cost of the COB components are identical to the

Mar/2015 distribution.

Pictures

Click on the pictures for enlarged details.

|

|

| HSIO-II |

Pixel Interface |

Requests for Joining Production Distribution

The unit cost for this round will be identical to the Mar/2015 production batch component costs as lised below,

but condensed the variations assuming HSIO-II:

| Item | Unit Price |

|---|

| HSIO-II with DTM and TTC mezzanines, but without transceivers | $4700 |

| HSIO Pixel interface board with 18 RJ45 I/O port | $1500 |

Following component orders will need checks for production arrangements before can be accepted:

| Item | Unit Price |

|---|

| COB motherboard with DTM, but without DPM mezzanines | $7400 |

| DPM dual-RCE mezzanine | $3700 |

| RTM (16xSFP) with TTC mezzanine, but without transceivers | $1800 |

Please fill in the RCE/HSIO request form

for the request quantities, fund contribution channel and delivery info and

send to Su Dong

by Jun/08/2016.

Apologies for the rather short time for collecting requests as many people have been waiting for this

make up production for quite some time and we are trying to get the production going asap.

For requests from US collaborators, the fund contribution can be managed by US

ATLAS internally. For international ATLAS requests, the fund contributions will

be collected by US ATLAS through CERN account transfers. An ATLAS Agreement will be drafted and signed

between each institution and SLAC+BNL before fund collection. The exchange

rate to convert the quote US$ amount to CHF will be according to the

CERN CET exchange rate

at the time of fund transfer. The delivery of completed boards can be direct shipped to your instituation

(which usually inovlves import tax to the receipient), or to pick up at CERN, as we expect

a group of them will be shipped to CERN together.

Some useful links:

Su Dong