## A Swift and Slim Flavour Tagger exploiting the CMOS Sensor Technology

#### M.Winter, on behalf of

IReS: A.Besson, G. Claus, C. Colledani, M. Deveaux, M.Dorokhov, W. Dulinski, M.Goffe, D. Grandjean, F. Guilloux, S. Heini, A. Himmi, Ch. Hu, K.Jaaskelainen, M. Pellicioli, A.Shabetai, H. Souffi-Kebbati, M. Szelezniak, I. Valin

(M6/M8 DAPNIA: Y. Degerli, E. Delagnes, N. Fourches, P. Lutz, F.Orsini)

- Reminder: main features and advantages of CMOS sensors

- Demonstrated performances and fabrication processes explored

- Specific aspects of a VD based on CMOS sensors

- Status of the main R&D directions:

- spatial resolution and ADC design

- thinning procedure

- radiation tolerance

- read-out speed

- Summary and Outlook

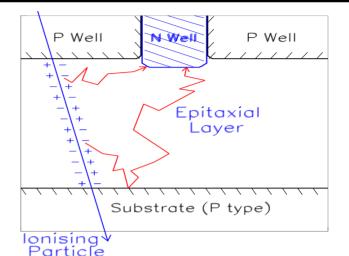

### Main features and advantages of CMOS Sensors

- Basic detection features:

- Signal charge  $\infty$  epitaxial thickness

- (~ 80 e<sup>-</sup>/h pairs /  $\mu$ m)

- N wells bound to be charge collectors

- Sensitive volume mostly unbiased (low resistivity Si)

- Main advantages w.r.t. other technologies:

- System-on-Chip (SoC)

- Sensitive volume (~ epitaxial layer) is ~ 10  $\mu m$  thick

- $\geq$  sensors may be thinned down to < 20  $\mu$ m)

- Standard, massive production, fabrication technology

- ➤ cheap, fast turn-over

# > Attractive trade off between granularity ( $\sigma_{sp}, \sigma_{2hits}$ ), material budget, read-out speed and radiation tolerance

LCWS-05, SLAC, March 2005

CMOS Strasbourg - Saclay

### Performances Achieved with MIMOSA chips

- 11 MIMOSA prototypes designed and fabricated since 1999

- 6 fabrication processes explored: AMS-0.6μm, AMI-0.35μm, AMS-0.35μm (opto and ordinary), IBM-0.25μm, TSMC-0.25μm

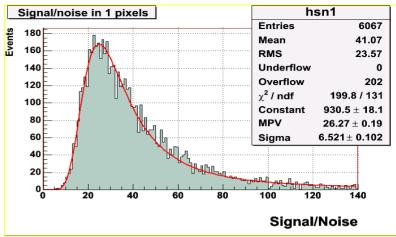

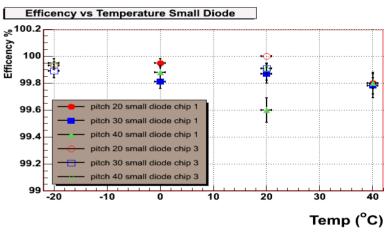

- Most chips tested with ~10<sup>2</sup> GeV/c π<sup>-</sup> (CERN-SPS)

- S/N ~ 20-30 (MPV) ⇒ε<sub>det</sub> ~ 99-99.9 %

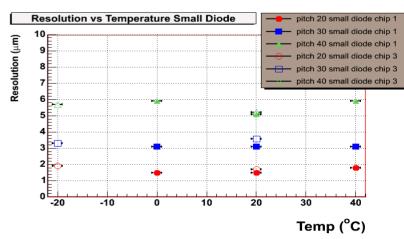

- $\sigma_{sp} = 1.5-2.5 \mu m$  (20 μm pitch) ;  $\sigma_{2hits} ≥ ~ 30 \mu m$

- Rad. Tol. For ILC conditions checked with neutrons and X-Rays

- Reticle size chip fabricated and working well (e.g. imager)

- Assessment of 50  $\mu\text{m}$  thinning under way

- Application to STAR, CBM, etc.

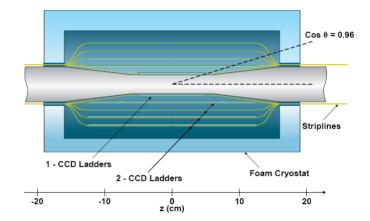

## Specific aspects of the CMOS VD concept

- Overall design a priori very similar to TESLA TDR concept (CCD):

- 5 cylindrical layer

- R = 15 60 mm

- surface ~ 3000 cm<sup>2</sup>

- Basic characteristics:

- sensor thickness

~ 25-50 μm

- total number of pixels

~ 300 millions

#### P<sub>diss</sub><sup>mean</sup> ~≤ 25 W (full detector; 1/20 duty cycle)

• operating T < 0° ?

| Layer | Pitch | t <sub>r.o.</sub>  | N <sub>lad</sub> | N <sub>pix</sub> | P <sub>inst</sub> diss | P mean |

|-------|-------|--------------------|------------------|------------------|------------------------|--------|

| LO    | 20 µm | <b>25 μs</b>       | 24               | 30M              | < 120 W                | < 6 W  |

| L1    | 25 µm | $\leq$ 100 $\mu$ s | 16               | 70M              | < 80 W                 | < 4 W  |

| L2    | 30 µm | <b>200 μs</b>      | 24               | 70M              | < 100 W                | < 5 W  |

| L3    | 35 µm | <b>200 μs</b>      | 32               | 70M              | < 110 W                | < 5 W  |

| L4    | 40 µm | 200 μs             | 40               | 70M              | < 125 W                | < 6 W  |

Main R&D effort concentrated on achieving fast CMOS sensors: large data flow ⇒ signal processing (sparsification) integrated/chip

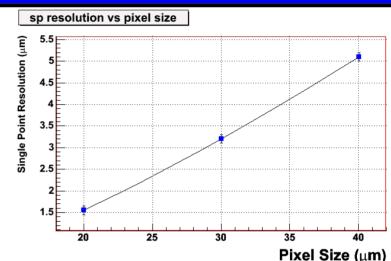

## Spatial resolution vs digitisation

Single point resolution of MIMOSA-9 as a function of pitch (~10<sup>2</sup> GeV/c π<sup>-</sup> at CERN-SPS)

> σ<sub>sp</sub> ~ 1.5 μm (L0) ~ 4 μm (L4)

with 12 bit ADC encoding

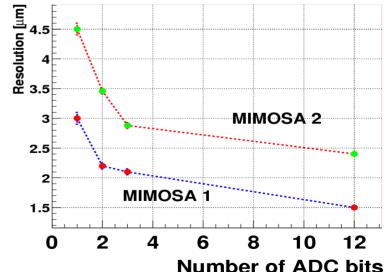

- Effect of digitising MIMOSA-1 & -2 charges on 1,2 or 3 bits

- >  $\sigma_{sp}$  ~ 2.5  $\mu$ m achievable after compact digitisation (3-5 bits)

- Design studies of fast ADC integrated at end of each column starting:

- Baseline: 4 bits

- Requirements:

20-40 μm x 1 mm; > 10 MHz; < 500 μW</li>

LCWS-05, SLAC, March 2005

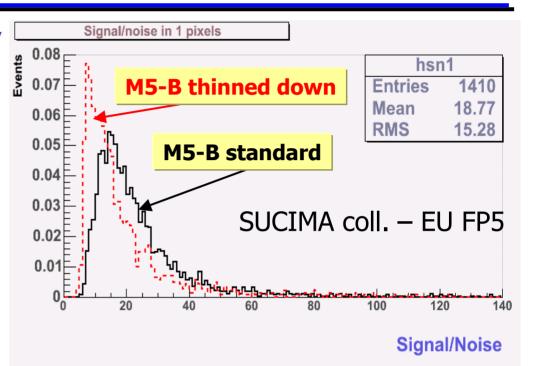

## The issue of thinning

- 120 µm sensor thickness repeatedly achieved on MIMOSA-5 wafers

⇒no performance loss observed (several chips tested)

- Goal: chip thickness ~ 25-50 μm (mounted on extra-light support)

- MIMOSA-5 chips thinned to 50 μm, outcome assessment under way via LBNL for STAR VD upgrade

- Substrate removal achieved with MIMOSA-5 (≥~ 15 µm thickness) for O(10 keV) electron detection (EB-CMOS) ⇒ detection efficiency drop observed (due to Q loss)

- Substrate removal is not (yet) the solution: optimal solution would be an etch stopper buried in the substrate at 25  $\mu m$  depth

- BUT: commercially not available today ⇒ under investigation

CMOS Strasbourg - Saclay

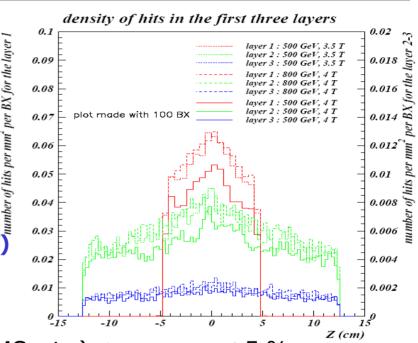

## Constraints from beamstrahlung background

- Characteristics (from Monte-Carlo !!!)

- e<sup>±</sup><sub>BS</sub> have essentially low momentum

⇒very sensitive to B<sub>exp</sub>=4T

> Only  $e^{\pm}$  with  $p \ge ~ 9 \text{ MeV/c}$ (resp. 16 MeV/c) reach L0 (resp. L1)

- $\sim \sim \le 5$  hits/cm<sup>2</sup>/BX at 90° (R = 15 mm, 4T)

- 1) Impact on read-out speed:

- $\blacktriangleright$  0.15 % hit occupancy in 25  $\mu$ s

- ▶ Cluster mult. (5-10), uncertainties (MC, etc.)  $\Rightarrow$  occup. ~≤ 5 %

- $\Rightarrow$  ~≤ 25  $\mu s$  needed in L0 and ~≤ 100 (50?)  $\mu s$  in L1

- 2) Impact on radiation tolerance w.r.t. non-ionising damage:

- $\Rightarrow 6.10^{11} \text{ e}_{\text{BS}}/\text{cm}^2/\text{yr} \Rightarrow 2.10^{10} \text{ n}_{\text{eq}}/\text{cm}^2/\text{yr}$  (NIEL factor ~ 1/30)

- ⇒ Uncertainties (MC, NIEL, etc.): ~≤ 1.10<sup>11</sup> n<sub>eq</sub>/cm<sup>2</sup>/yr (Ionising damage less worrying: ~ 15-50 kRad/yr)

## The issue of radiation tolerance

- Non ionising damage:

- 1) Neutron gas:

- M.C. prediction ~ 10<sup>9</sup> n<sub>eq</sub>/cm<sup>2</sup>/yr

- > MIMOSA-1/-2 tests (DUBNA):  $\sim \le 10^{12} n_{eq}/cm^2$  acceptable

- > <u>Required tolerance</u> should account for uncertainties (safety factor of 10) and ≥~ 3 years of running: ~  $3.10^{10}n_{eq}/cm^2$

- 2) Beamstrahlung e<sup>±</sup>:

- > M.C. <u>prediction</u> ~  $6.10^{11} e_{BS}/cm^2/yr (2.10^{10}n_{eq}/cm^2/yr)$  in L0

- Accounting for uncertainties (M.C.,etc.)

- $\Rightarrow$  <u>Aim for tolerance</u> to  $\sim \le 10^{13} \text{ e}_{\text{BS}}/\text{cm}^2$  ( $\sim 3.10^{11} \text{n}_{\text{eq}}/\text{cm}^2$ )

2 MIMOSA-9 chips exposed to  $3.10^{12}$  and  $10^{13}$  e<sup>-</sup>/cm<sup>2</sup>: analysis under way

### • Ionising damage:

- e<sub>BS</sub>: M.C. <u>prediction</u> ~ 15 kRad/yr

- <u>Aim for tolerance</u> to 150 kRad (3 years, including uncertainties)

- MIMOSA chips exposed to 10 keV X-Rays: no perfo. loss for several 100 kRad

- Proto. designed for bio-medical imaging (SUCIMA FP5), with dedicated features against rad. damage, stands 1 MRad (X-Rays) without significant loss

- New prototype being fabricated (MIMOSA-11), equipped with various pixel architectures exploring sources of ionising radiation sensitivity

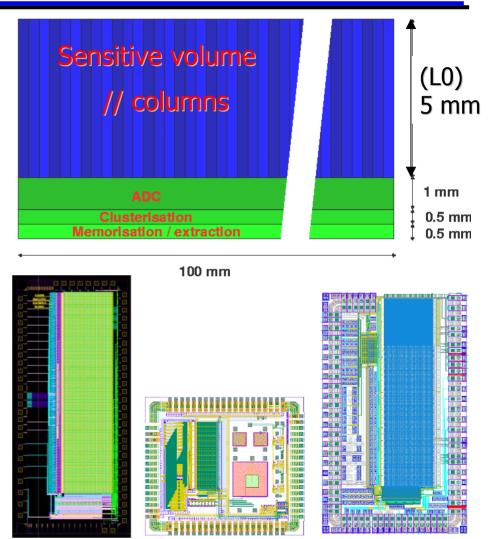

## Achieving high read-out speed

- Fast read-out required in L0 (and L1) ⇒massively // processing

- Ladder subdivided in short columns (⊥ to beam) processed in // (serial treatment of pixels inside each col.)

- Large data flow

data sparsification integ. on chip

- Develop progressively full r.o. chain on col. par. prototypes:

- Inside each pixel: CDS with preAMP (cf MIMOSA-6, -7, -8)

- End of each column: ADC + cluster finding + sel. info extraction

MIMOSA-7

#### MIMOSA-6 CMOS Strasbourg - Saclay

LCWS-05, SLAC, March 2005

MIMOSA-8

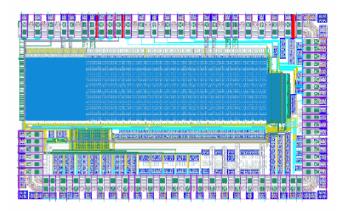

## Achieving high read-out speed (2)

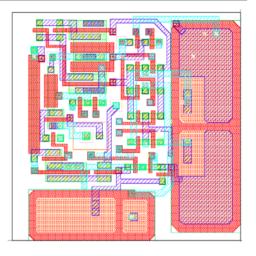

- MIMOSA-8 (designed in 2003 with DAPNIA)

- TSMC 0.25  $\mu$ m digital fab. process with 8  $\mu$ m epitaxial layer

- 32 // columns of 128 pixels

- Pixel pitch: 25 μm

- 4 sub-arrays featuring AC and DC coupled on-pixel voltage amplification

- On-pixel CDS

- Discriminator at end of each column

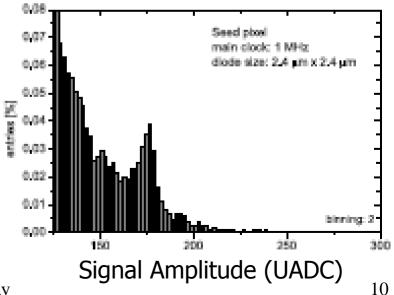

- Test with <sup>55</sup>Fe source:

- Very encouraging results

- Conversion factor: 50-110 μV/e-

- Pixel noise (including CDS) ~ 13-18 e<sup>-</sup> ENC !

- Low pixel-to-pixel dispersion

- Architecture seems worth extending with integrated ADC, a.s.o.

LCWS-05, SLAC, March 2005

CMOS Strasbourg - Saclay

## Achieving high read-out speed (3)

- $e_{BS}^{\pm}$  rate is ~ 25 times lower in L2 than in L0  $\Rightarrow t_{r.o.} \sim 200 \ \mu s \Rightarrow \sim 5$  frames / train

- 2 phase micro-circuit architecture, reducing the data flux:

- Charge sampled and stored inside pixel during train

⇒ 5 capacitors integrated in each pixel

- 2) Signal processed in between trains

- 1<sup>st</sup> multi-capa. pixel: MIMOSA-6 (design with DAPNIA in 02) Test results: ⇒Large pixel-to-pixel dispersion

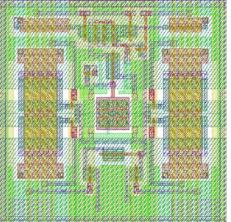

- MIMOSA-12: new prototype exploring various types & dimensions of memory cells (scheduled for fab. 25 March)

- AMS-0.35  $\mu m$  techno.

- 4 capacitors/pixel (35  $\mu$ m pitch)

- 6 sub-arrays, exploring various MOS capa.: 50, 100, 200 fF

- ⇒ Aim for minimal size capacitors providing satisfactory precision, depending on pitch - i.e. layer - (~ 4.6 fF/µm<sup>2</sup>)

### Summary and Outlook

- Concept of vertex detector using features of CMOS sensors progressing, based on requirements accounting for uncertainties (e<sub>BS</sub> !)

- Well established performances:

- **S/N**, ε<sub>det</sub>, σ<sub>sp</sub>

- Rad. Tolerance to neutrons and X-Rays

- 120  $\mu m$  thinning of Megapixel sensors

- Most recent achievements

- Fast col. // pixel architecture (integrated CDS) found, with low noise (< 20 e<sup>-</sup> ENC) and small pixel-to-pixel dispersion

- Assessment of a well performing R&D fabrication process:

AMS-035 μm (opto and epi-free) ⇒ very good perfo. even with 40 μm pitch (L4)

- Checks of tolerance to 10-20 MeV electrons under way

- Outcome of thinning to 50  $\mu$ m under study ( $\geq \sim$  15  $\mu$ m not yet OK)

- Next important steps:

- 1) Fast column // sensor with digital output, adapted to L0-1 (integrated low power, fast and compact 4-bit ADC)

- 2) New multi-memory cell sensor adapted to L2-4

- Complete study of MIMOSA-5 thinning to  $\sim$  50  $\mu$ m with LBL

- Investigate characteristics of new fab. processes (e.g. IBM-0.13  $\mu$ m, UMC-0.18  $\mu$ m)

- Thinning no-epi sensors is very appealing: any possibility ?

- Privileged contact with a foundry would be very valuable...

- > Aim for a fast col. // megapixel proto providing digital output in 2007